## **Electronics III**

Most of the theory and equations mentioned in these lectures were taken from these following references:

- Adel S. Sedra, Kenneth C. Smith, "

Microelectronic Circuits ", 5<sup>th</sup> edition 2004.

- Donald A. Neamen, "Microelectronic Circuit Analysis and design ", third edition 2007.

- Jacob Millman, Arvin Grabel, "Microelectronics ", second edition 1987.

- Clifton G. Fonstad, "MICROELECTRONIC DEVICES AND CIRCUITS" 2006

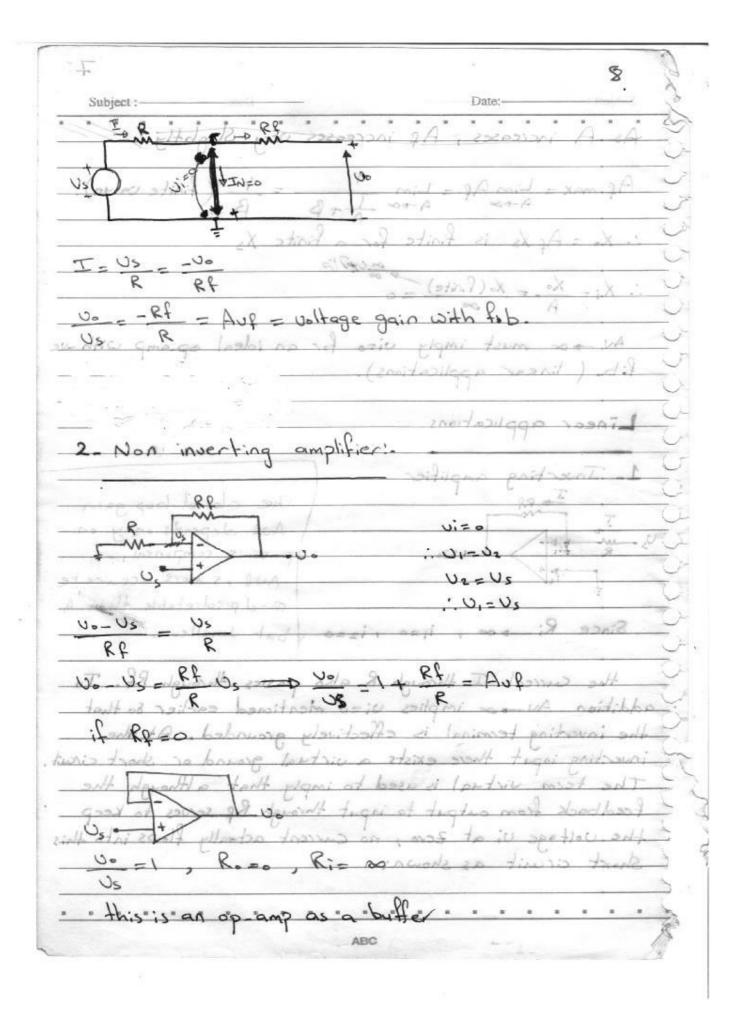

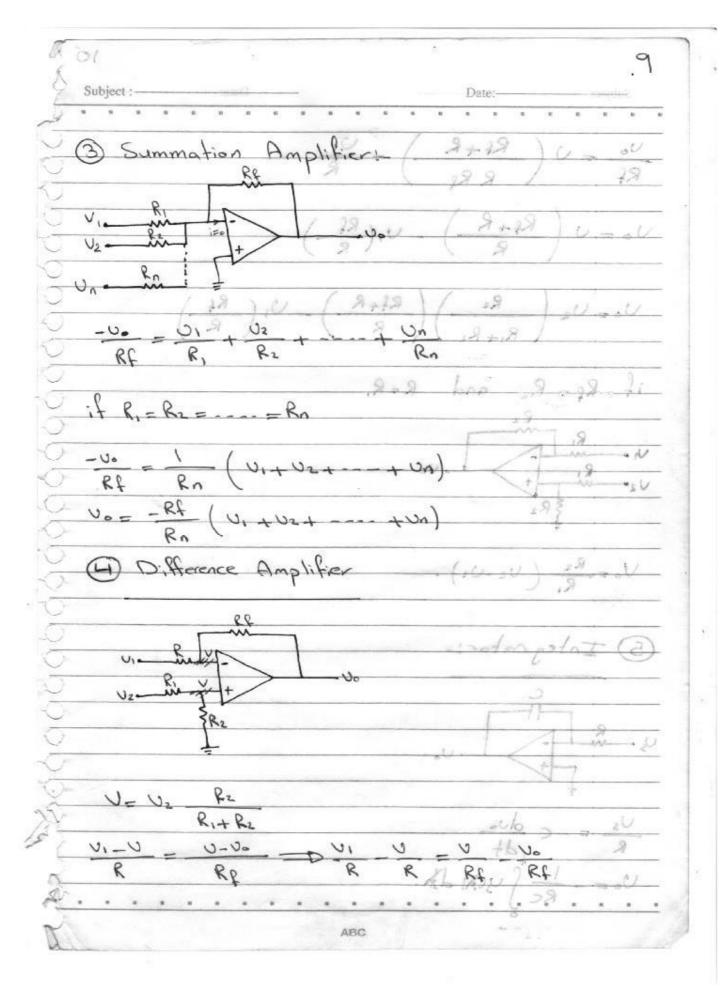

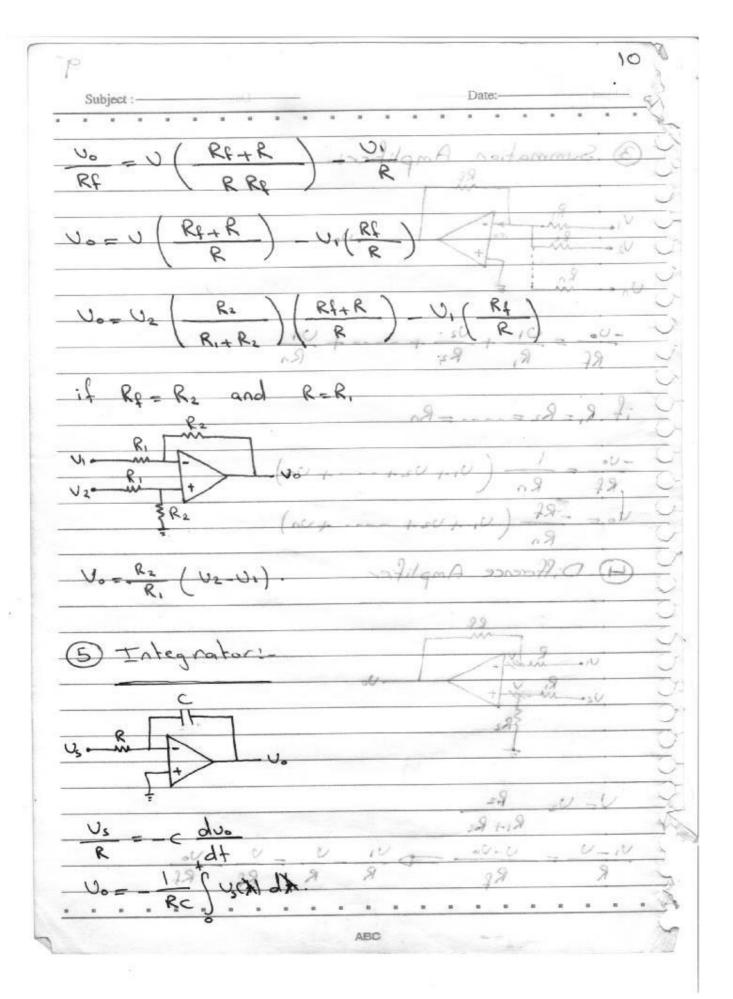

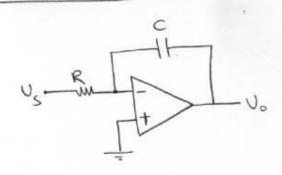

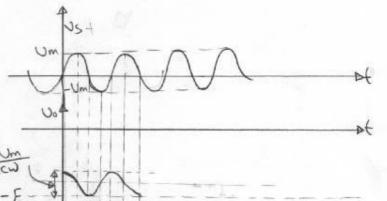

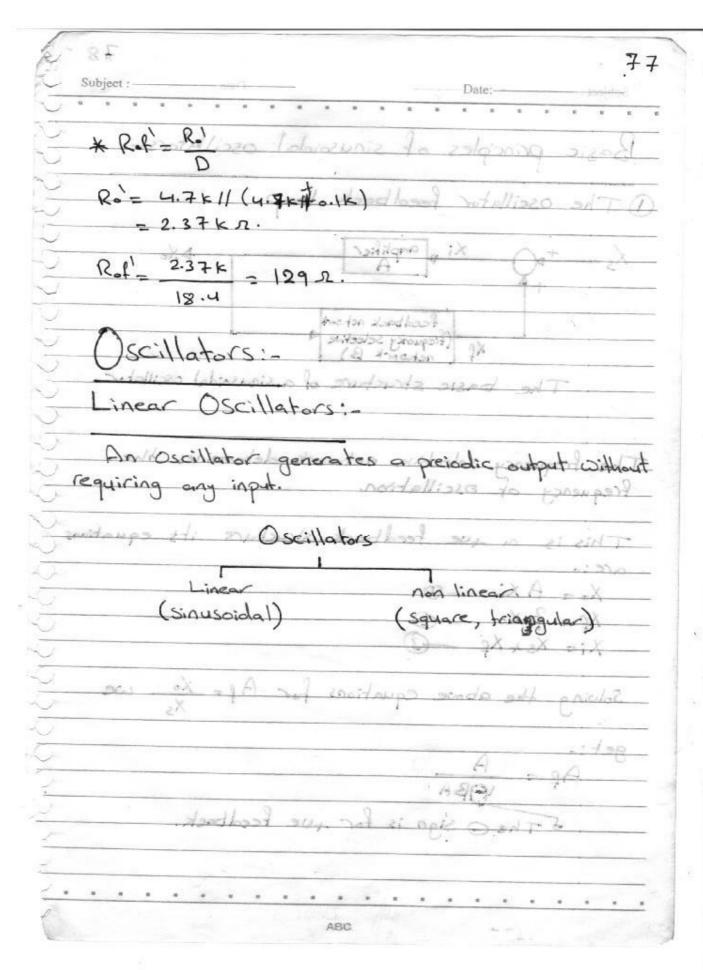

## Miller Integrator:

\* At Dic (W=0) the capacitor behaves as an open cct., there is no negative feedback.

\* This is very important in the integrator cct. and is a problem, because any tiny DC Component in the input signal will theoretically produce an infinite output. Of course, no infinite of p voltage results in practice, rather the ofp of the op-amp. Saturates at a voltage close to the op-amp. of the op-amp. Saturates at a voltage close to the op-amp. the or-ve power supply depending on the polarity of the

input D.C signal.

Vo(iw) = -1

Vs(iw) = jwRC (transfer c/c's of the Miller

Theoretor).

for exemple !-

Us = Um sinut + E , E-DO (Eis +ve)

Vo = Vm Coswt - Et RC

E: - Saturation voltage of the op-amp.

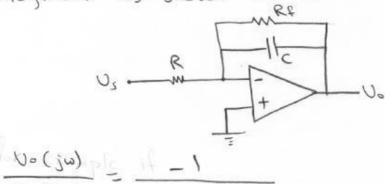

To avoid this problem a resistor is added in perallel with the capacitor. If Rf >> Xc the new circuit will be as close to the Miller Integrator as Possible. The new circuit is called the D.C clamped integrator as shown below:-

if

$$\omega = o(D,c)$$

then  $\frac{O_0(j\omega)}{O_0(j\omega)} = \frac{-Rt}{R}$

if  $\omega \neq o$  the  $\frac{O_0(j\omega)}{O_0(j\omega)} \approx \frac{1}{-1}$  since RETRIXC

for example :-Us = E + Um sinut. (E-00) Eis +ve Uo B-ERF + Um coswt

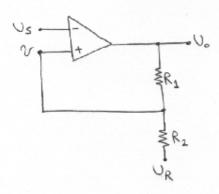

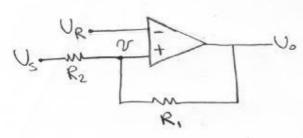

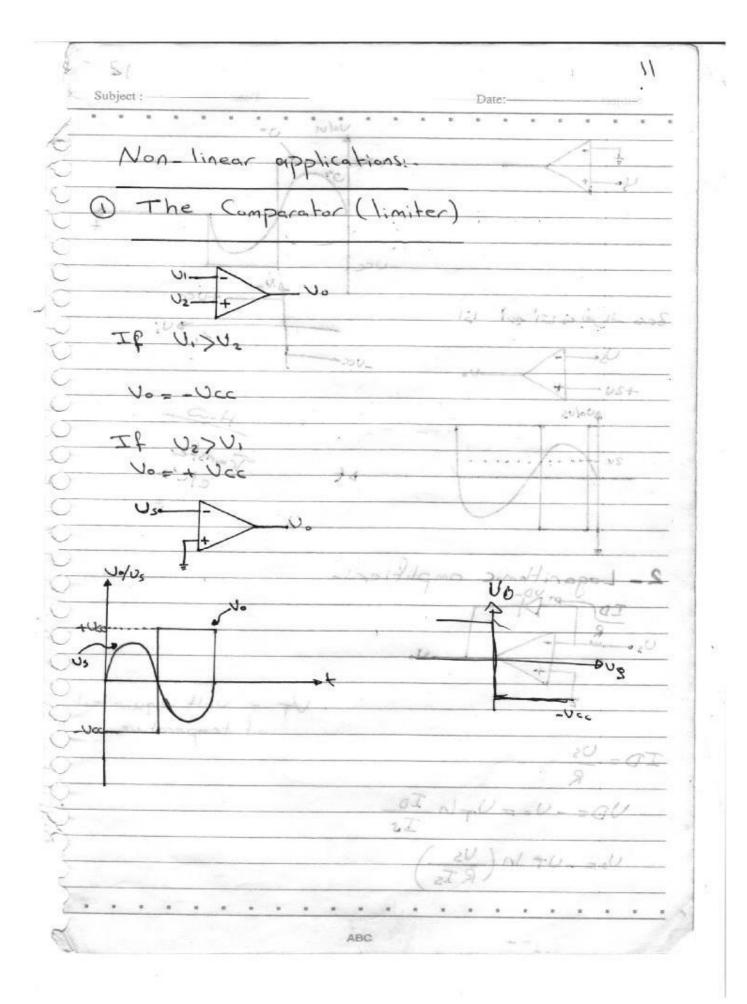

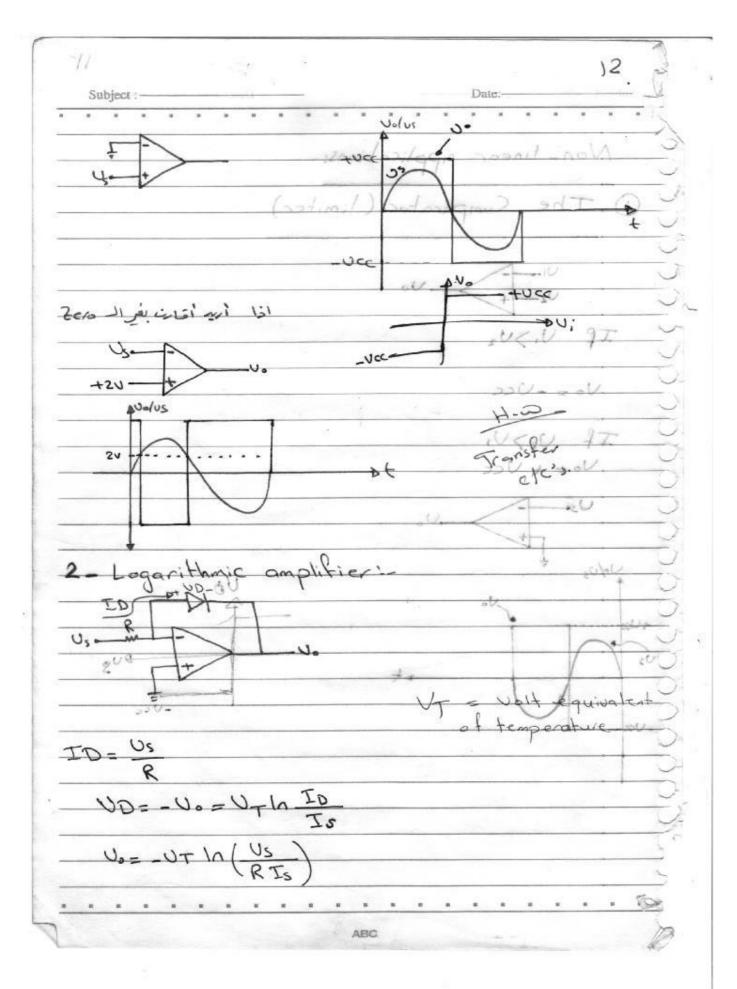

Regenerative Comparator (schmitt trigger):-

a Inverting Schmitt trigger

Assume that Us < V so that Uo=+E. The vollage V can be found by using superposition:

$$V = V_R \frac{R_1}{R_1 + R_2} + V_0 \frac{R_2}{R_1 + R_2}$$

In this case  $V = VR \frac{R_1}{R_1 + R_2} + E_0 \frac{R_2}{R_1 + R_2} = V_1$  = Constant.

If Us increases until Us = V1, then Vo = - E

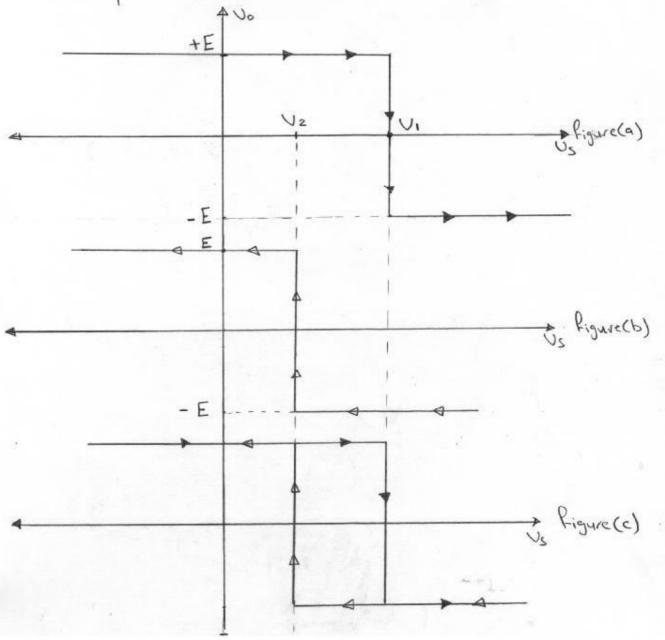

The transfer c/c's of this case is as in figure (a),

note: E is the saturation voltage of the op-emp.

Now  $V_0 = -E$  and  $V = V_R \frac{R_1}{R_1 + R_2} - E \frac{R_2}{R_1 + R_2} = V_2 = constant$   $V_2 < V_1$

If Us idecreases until Us=V2, then Vo=+ E.

The transfer c/c's of this case is as in figure (b).

The Complete transfer c/c's is as in figure (c).

UH = V1 - U2 = Hysterisis

## (b) Non - Inverting Schmitt trigger

Assume that v < VR, Vo=-E,

In this case

$$V = U_{S} \frac{R_{1}}{R_{1} + R_{2}} + -E \frac{R_{2}}{R_{1} + R_{2}}$$

$$V_s \frac{R_1}{R_1 + R_2} - E \frac{R_2}{R_1 + R_2} < V_R$$

$$V_S < \left( V_R \frac{R_1 + R_2}{R_1} + E \frac{R_2}{R_1} \right) V_1$$

If Us increases until VIUR and Us=U, then  $V_0 = +E$ . The transfer c/c's is as in figure (a).

Now No=+E and

and US 7, UR R, +R2 - E R, R2 - V2 If Us decreases until VKUR and Us & V2 then Uo = - E The transfer cl c's of this case is shown in figure (b). The Complete transfer c/c's is shown in figure (c). +E V2 J. Figurela) -E +E Je figurecls) +E Figure (c) -E

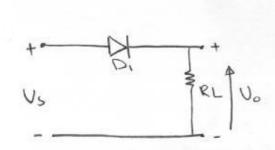

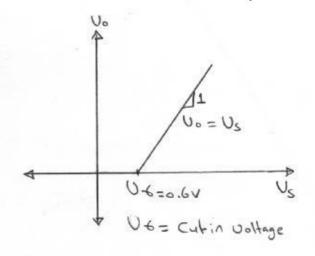

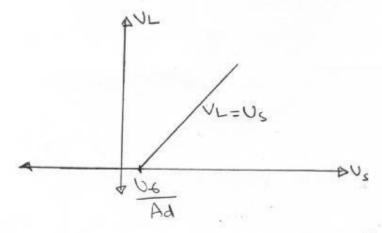

## Half-Wave Rectifier 1-

Half-Wave rectifier using a diode only.

So we will use the following circuit to rectify vollages less than 0.6 v:

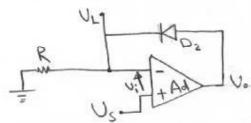

Half-wave rectifier using an op-amp.

UL: - the output of the rectifier

Diode D2 is not conducting when vox Ux and UL=0.

: Vi= Us

and Adus < U6

Now if Us increases until Uo > U6 and Us > U6 then Dz Conducts and UL=Us.

So voltages in milivolt range can be rectified

23

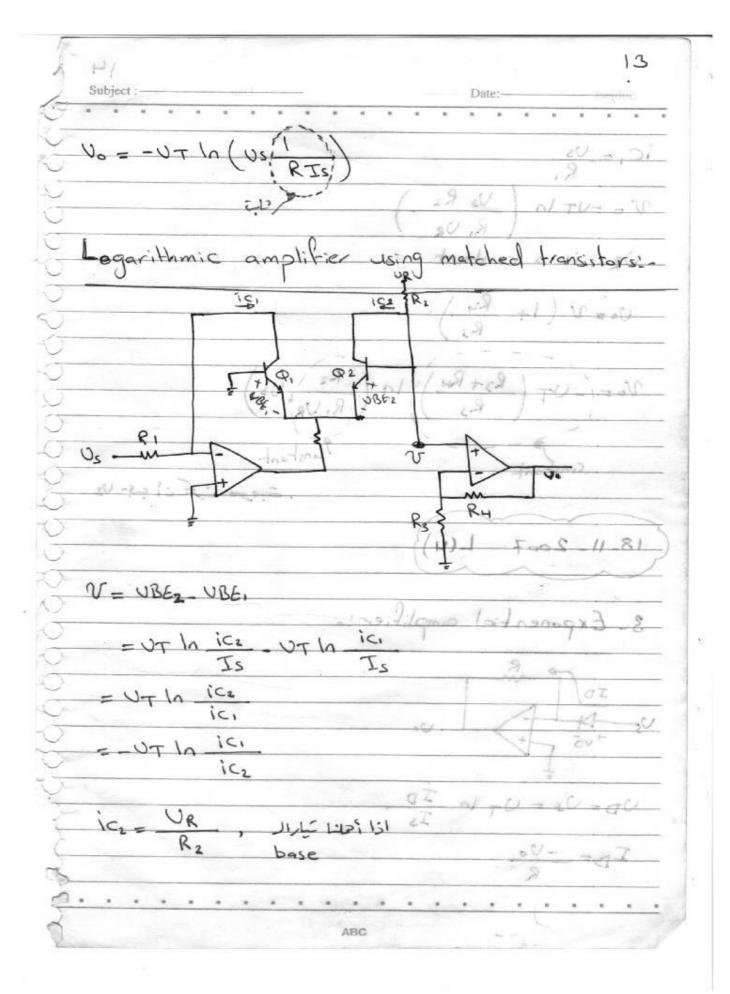

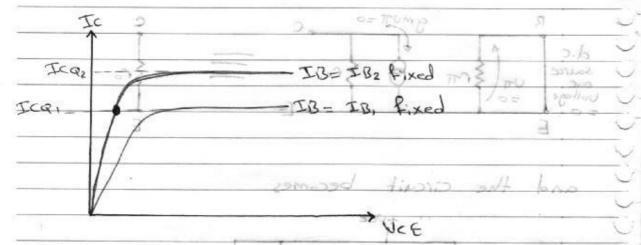

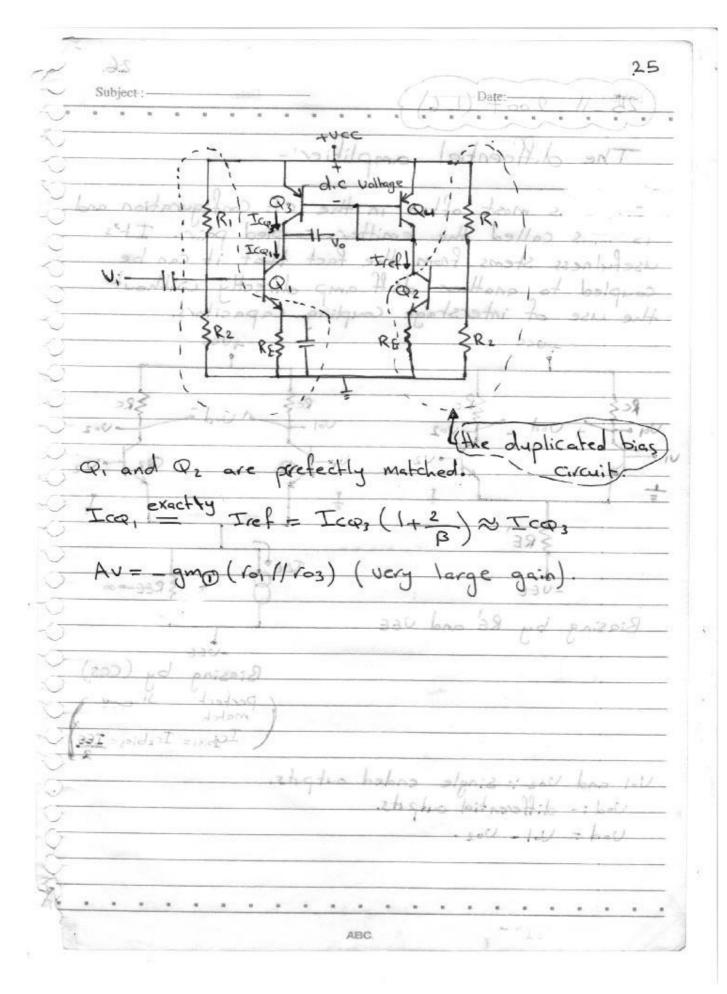

assume Icoz > Ico. to upo bod outon

note:

Jan 1907 =

Ica, must be exactly equal to Icaz. If they differ, the lower current will flow and the transistor with the originally higher current will be drewn into saturation. To achieve this equality we duplicate the biase circuit of the amplifier and use the duplicate to biase the ccs (active load) via a current mirror.

We do so because, for an IC, we may

comfortably assume that devices and components of the same shape and size will have the same characteristics.

ABC

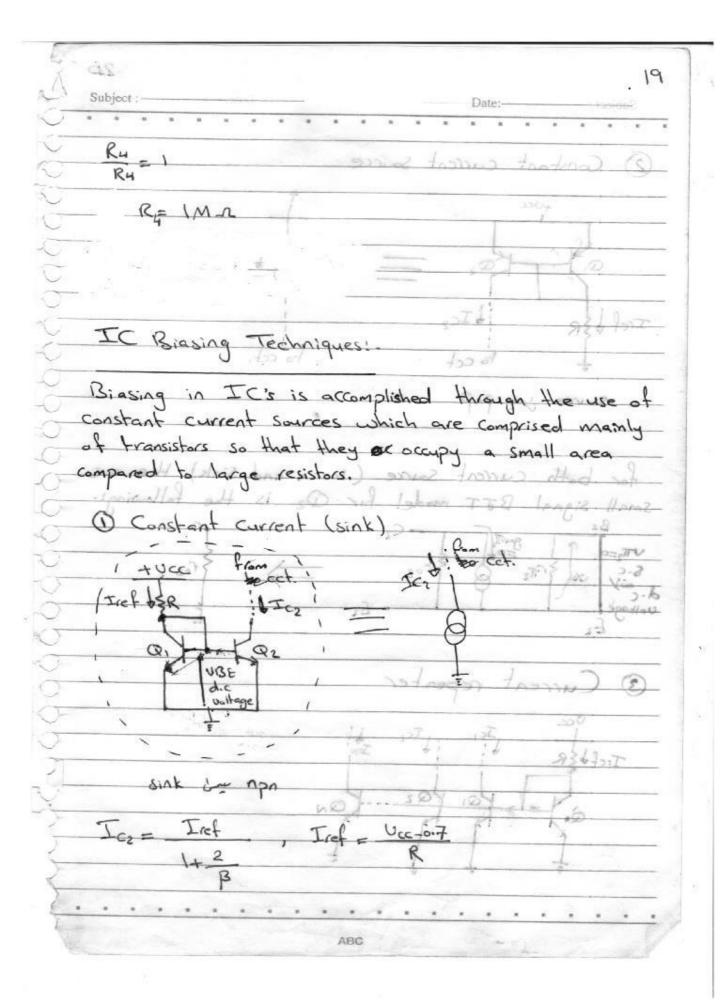

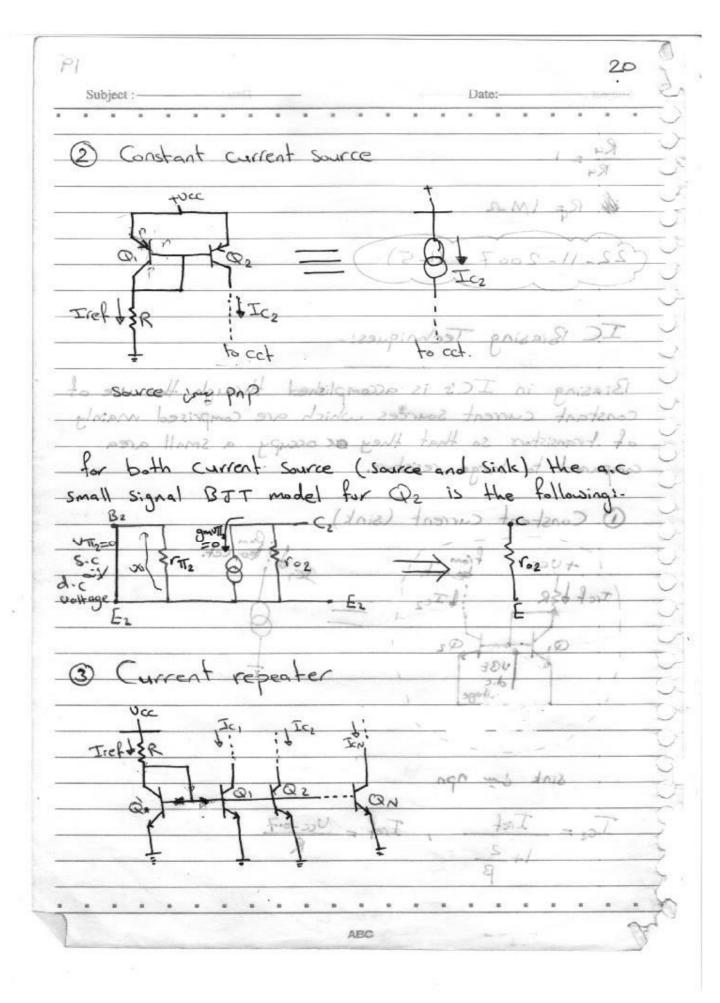

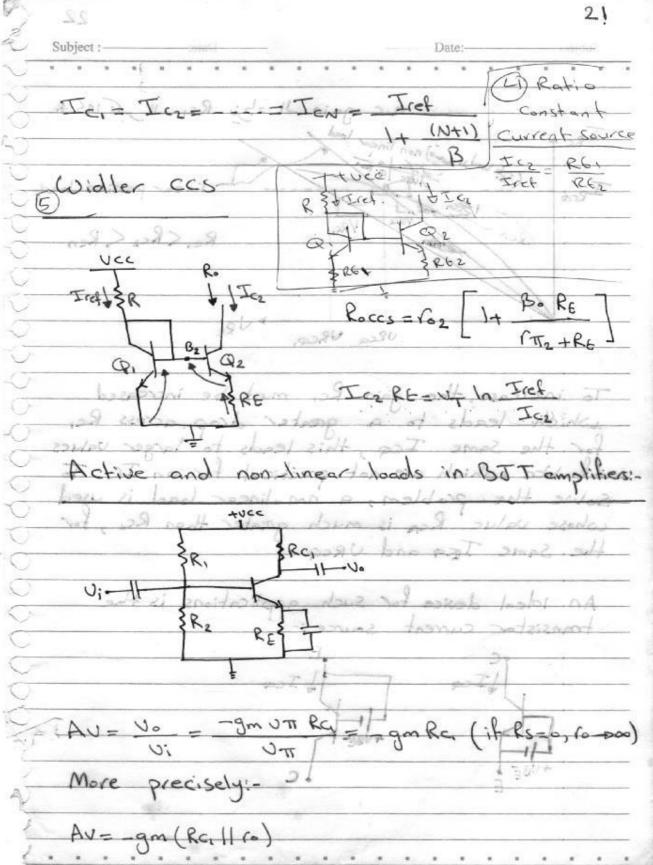

Bissing

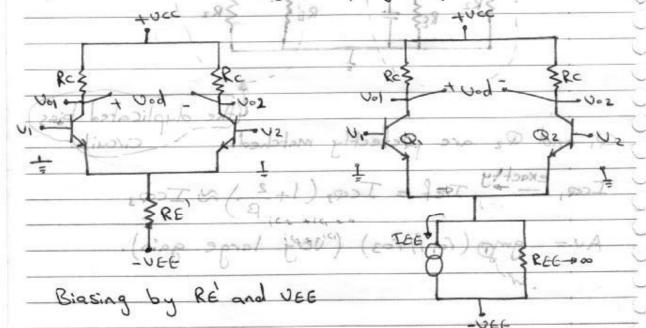

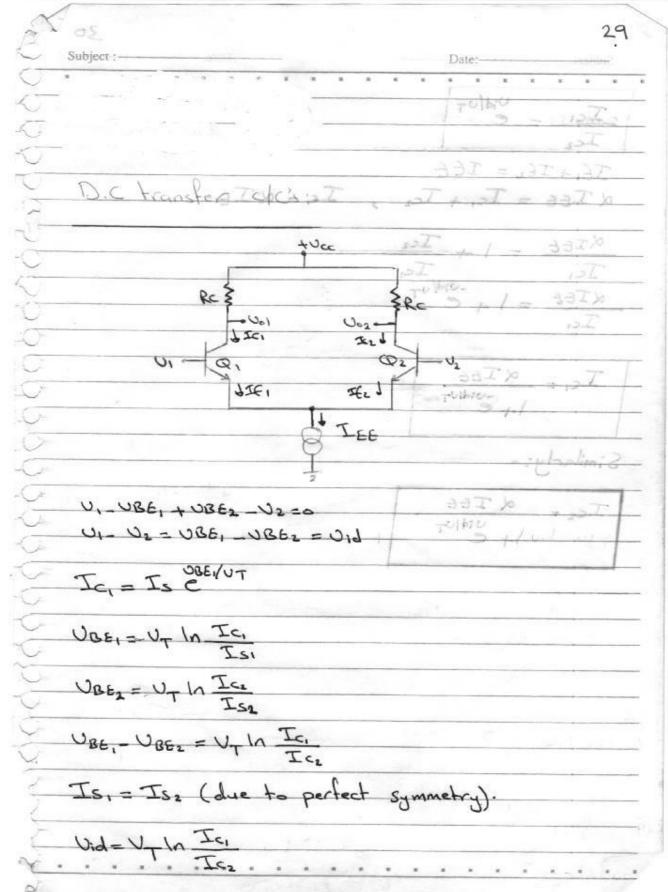

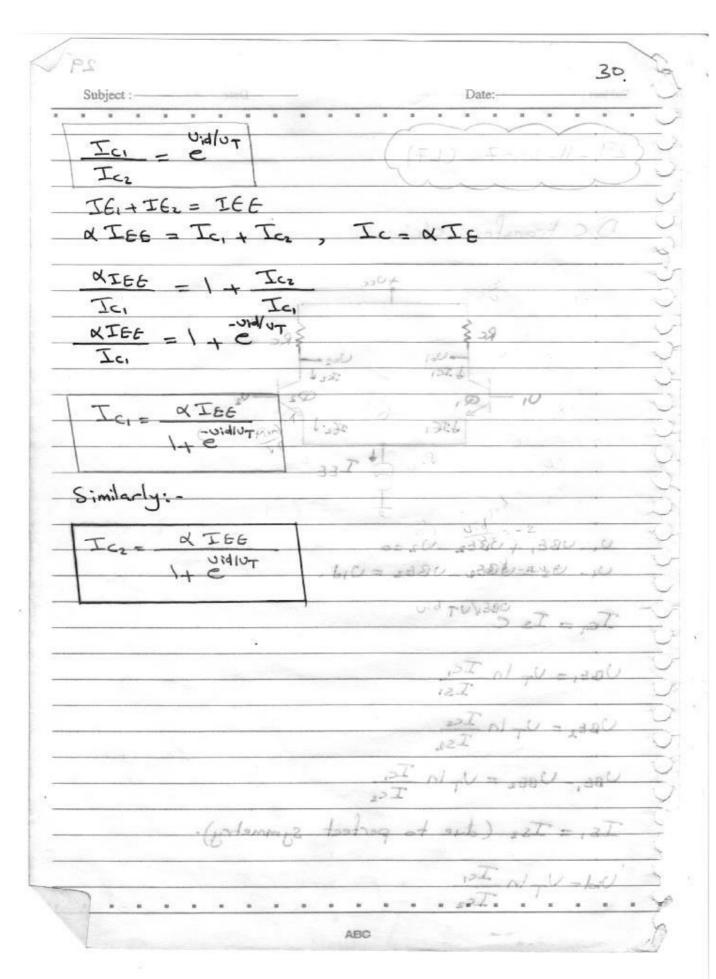

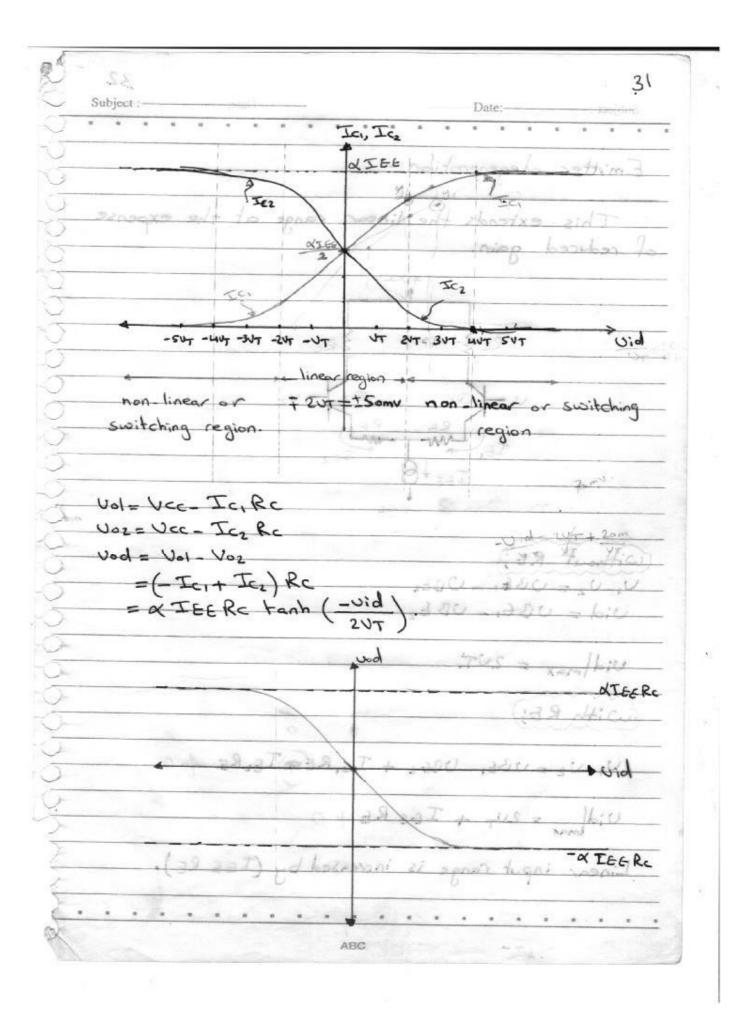

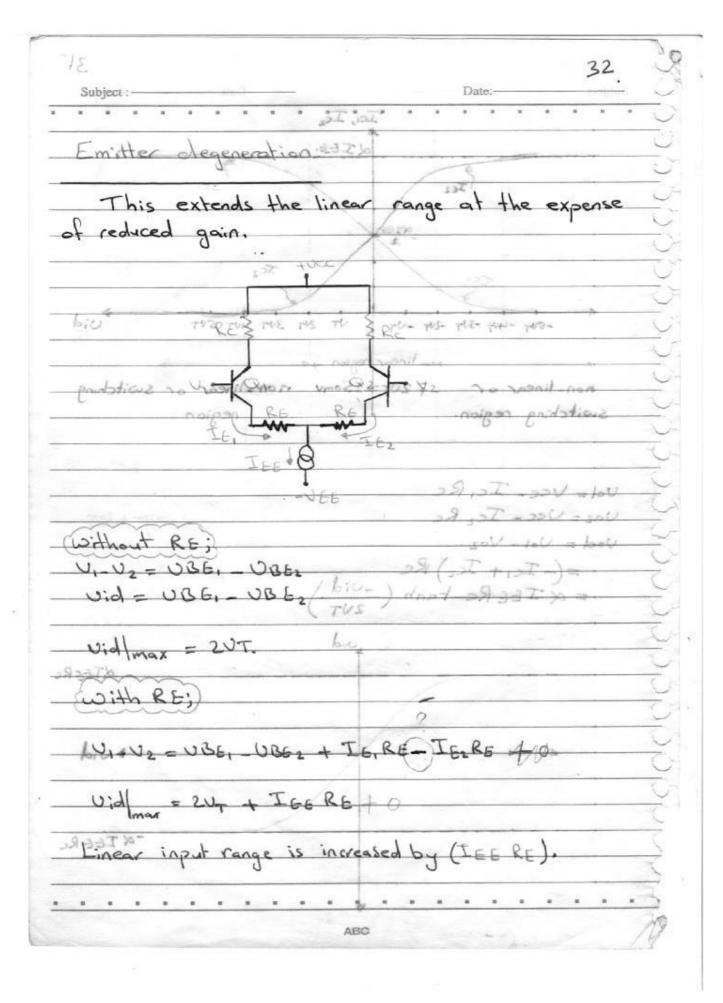

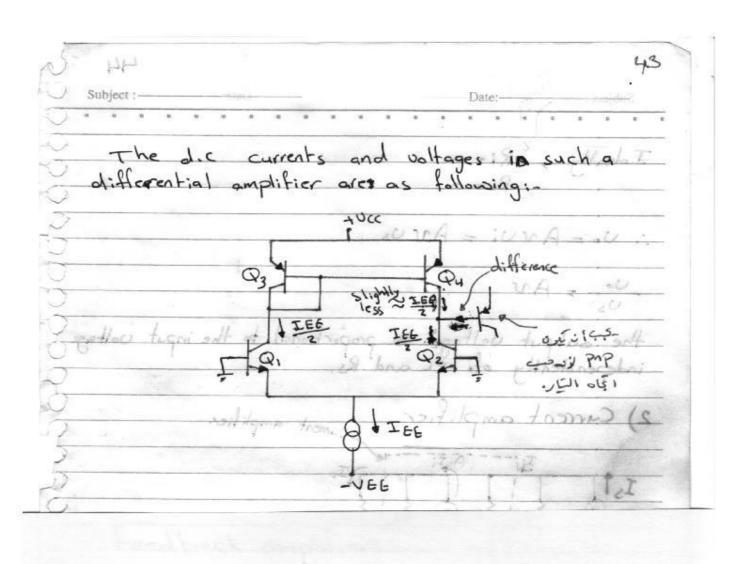

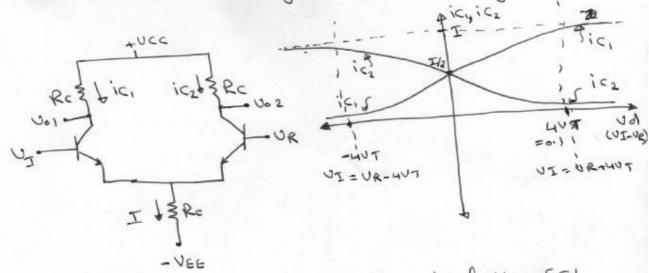

The differential amplifier:

52

This is most often in the CE Configuration and is thus called the emitter-coupled pair. It's usefulness stems from the fact that it can be coupled to another diff-amp directly without the use of interstage coupling capacitors.

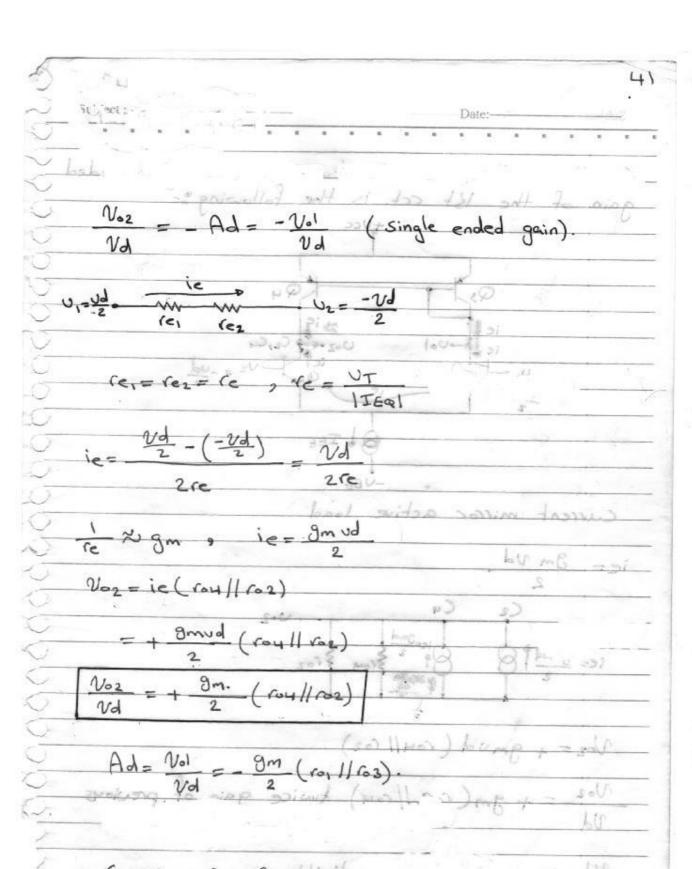

Vol and Voz: Single ended outputs.

Vod: - differential outputs.

Vod = Vol - Voz.

ABC

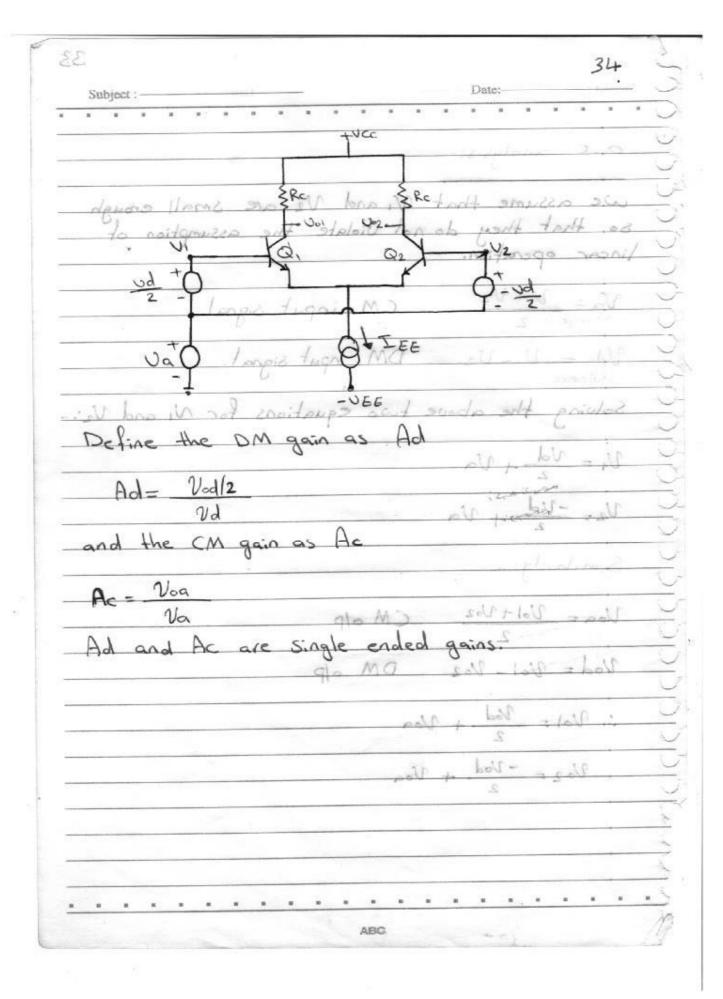

Ad = -9mRc 2

Subject:

Date:

Ac = CM gainnotzias qli alon nomo

Ac= Noa Va

Using one half of the cot.

Voa = - gm VTT, Rc

= -9 Rc (ib, x Th,), (Th, = 1/12 = 1)

= -B. Rc Va (+ 2 REE (1+B.)

Ac = - B. Rc , B. = 9m Fm

(TT + 2 REE Ba (1+ 1)

= 3m (11 ... > ...

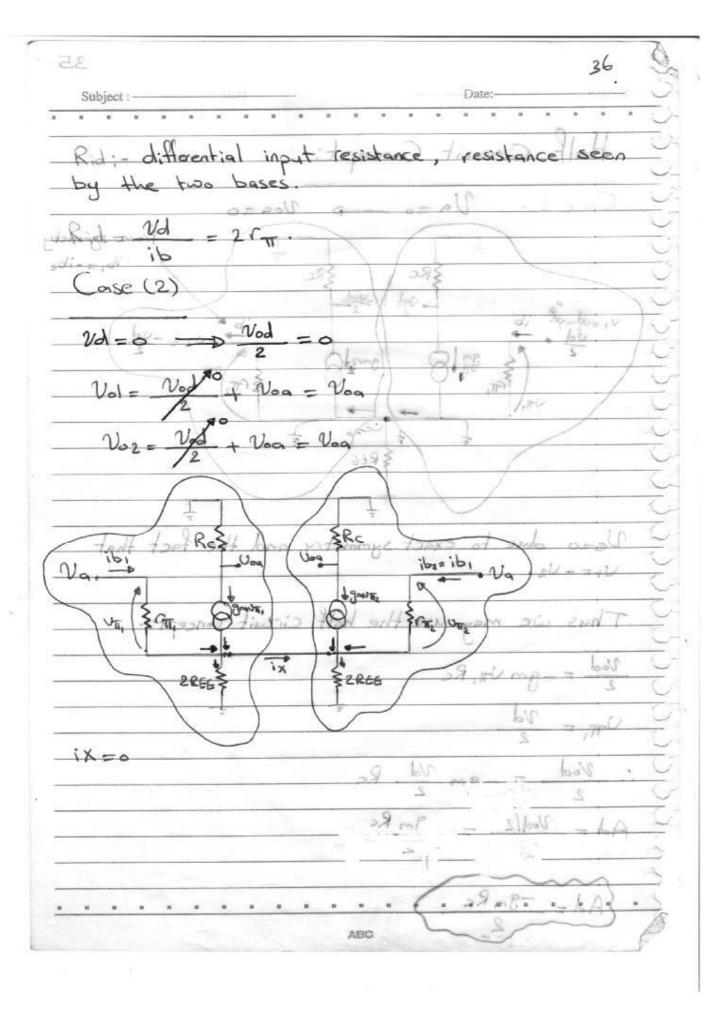

MRR

$A_{c} = -9m Rc$   $1 + 2 gm REE (1 + \frac{1}{Bo})$

for an ideal ccs, REB DOS

Ac -so

ABC

Subject: -

Date:-

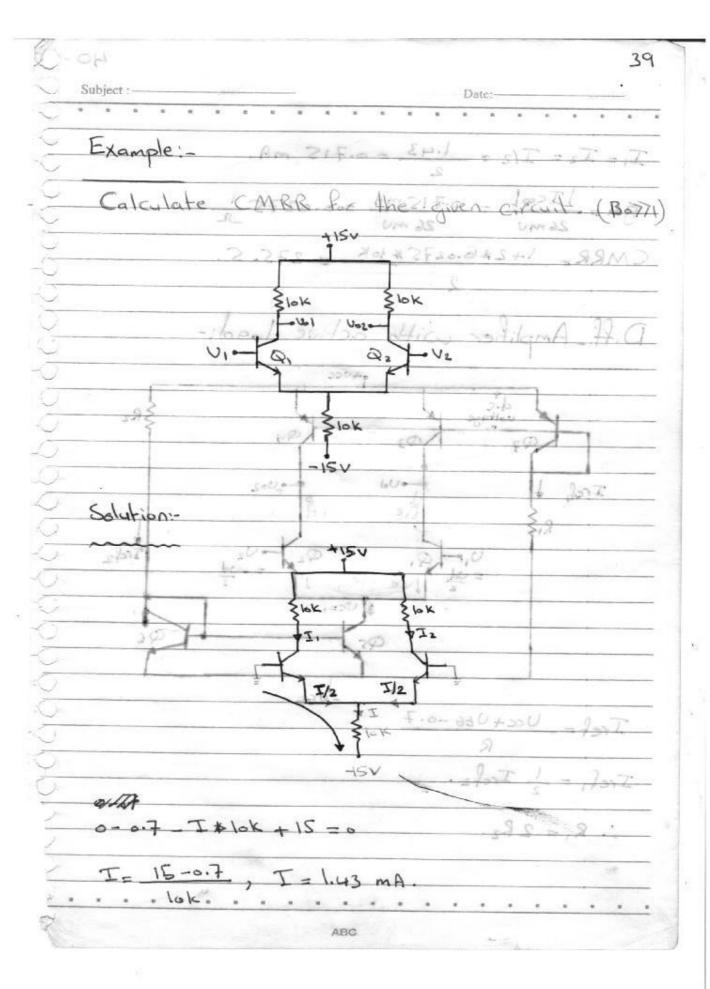

II= I2= I/2 = 1.43 = 0.715 mA

1Icol - 0.715mA 26 mu

CMRR \_ 1+2 \* 0.0275 \* lok

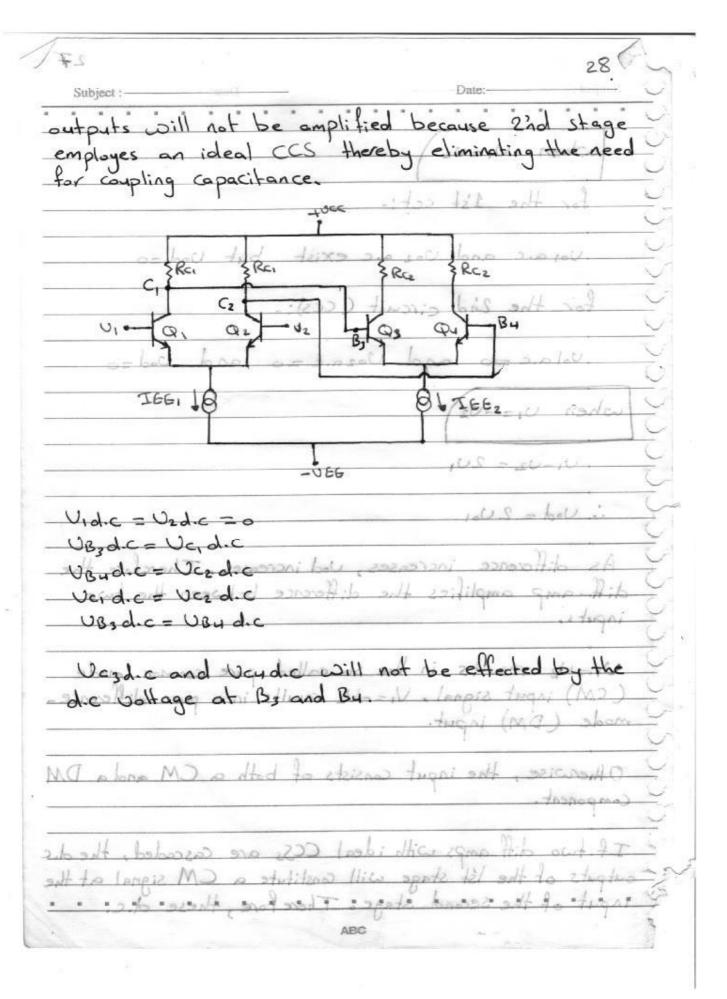

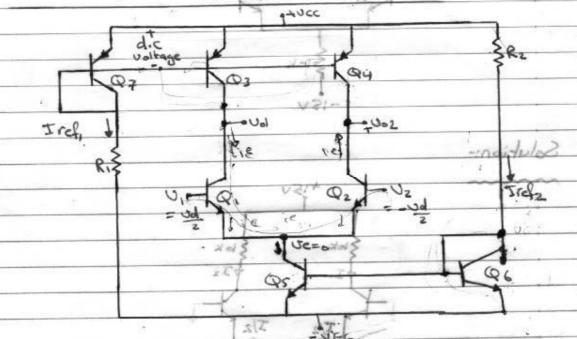

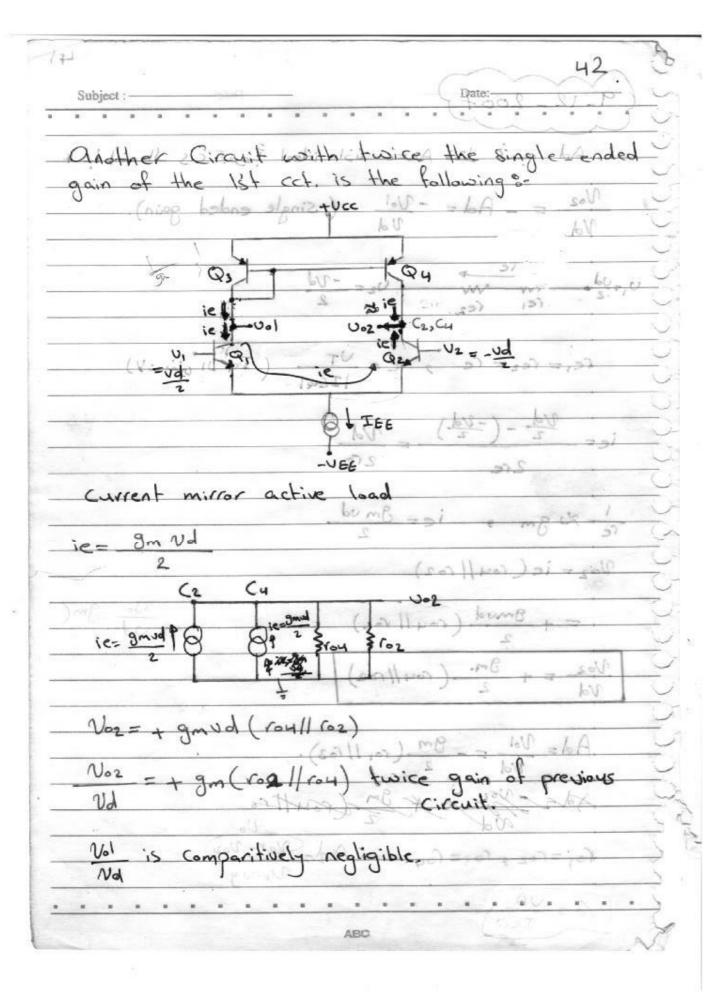

Diff - Amplifier with active

$Iref = \frac{V \times + V \times 66 - 0.7}{R}$   $Iref_1 = \frac{1}{2} Iref_2$

: R, = 2R2.

F.o- 21

for = roz, roz= foy digit

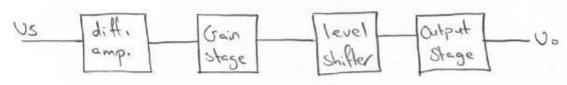

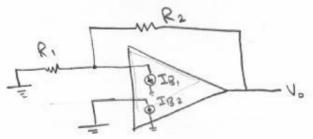

#### Operational Amplifier Specifications:-

- 1) Offset voltages and input bias current :-

- @ Offset voltage

Block diagram of the op-amp.

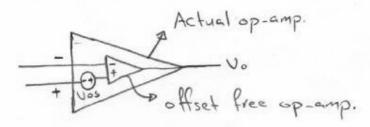

Mismatches between input devices of the diff-amp. Stage may create an output voltage with zero input, this voltage is called the output offset voltage (Vos) for an open looped op-amp.

Vos has a typical value of (1-5mu)

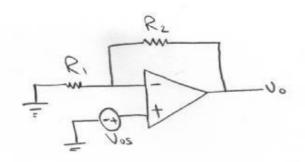

cct. model for an op-emp. with input offset voltage

To find the effect of the offset voltage: - the input voltage signal source is short circuited. following this procedure, we get the cct. Shown below (for the inverting and non-inverting op-amp. Configuration):-

Vo = (1+ R2) Vos

## Offset voltage Compensation:

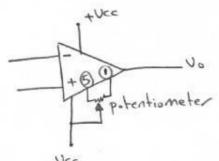

@ An op-amp. with offset-null terminals:-

1 and 6 are offset- null terminals.

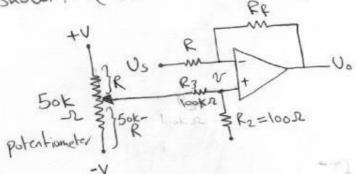

(B) An externally connected affset compensation network

Another method is by applying a small DC vollage at the

Another method is by applying a small DC vollage at the

input so as to cause the D.C output vollage to become

input so as shown: (For the inverting op-amp.)

Zero as shown: (For the inverting op-amp.)

$$-15\frac{R^2}{R_3+R_2}< V<+15\frac{R_2}{R_3+R_2}$$

if  $V=15V$ .

-15mu (V < +15mv

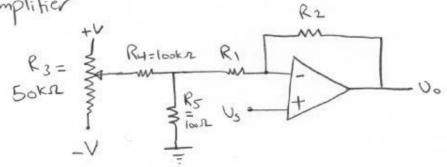

Offset voltage Compensation for the non-inverting amplifier R2

## 1 Input Bias Currents

the input bias currents are usually specified by their average value (IB) which is called the input bias current:

and by their difference which is called the input offset current, and is given by:

\* Typical values for op-amps using BJTs are IB = 100nA, and Ios = 10nA.

\* For an op-amp, using FETs (in the order of picoamperes).

To see the effect of the biasing currents on the operation of the op-amp. To do this, the signal source is grounded and we obtain the cct. Shown below: - (for the inverting and non-inverting op-amp).

Uo= IB, R2 为 IB R2.

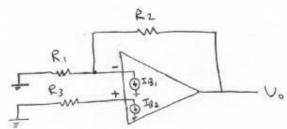

The effect of the biasing currents on the old D.c. Wolfage can be reduced using a simple compensation technique is done by technique. This compensation technique is done by adding a resistor (R3) in series with the non-inverting input terminal as shown:

$$I_{B_1} = I_{B} + \frac{I_{os}}{2}$$

$$I_{B_2} = I_{B} - \frac{I_{os}}{2}$$

Vo (due to IB) = Zero

$$V_0(\text{due to } \text{Ios}) = R_2 \frac{\text{Ios}}{2} + \frac{\text{Ios}}{2} R_3 R_2 \left(\frac{R_1 + R_2}{R_1 R_2}\right)$$

if  $R_3 = R_1 \parallel R_2$

then Vo(due to Ios) = Ios Rz

Vof offset voltage + biasing currents) = Ios R2 + Vos (1+ R2).

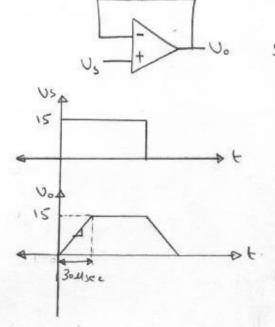

(2) Slew Rate:.

The slew rate is the maximum rate at which the ofp changes with time.

#### Example:

SR= 0.5 U/Msec.

if Us = Um sinut, is applied to a voltage Pollower Vo = Um sinut.

two = um w coswt.

dvo/max = Um W

( Um W)

The maximum rate at which the output changes, occures as the curves cross the Zero axis.

If (wom) > SR, then the olp is distorted.

fmax = SR (fmax is the maximum frequency without distortion of the output).

as Um changes, frax changes.

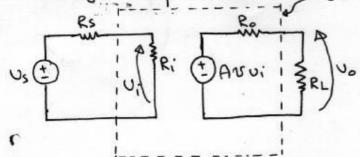

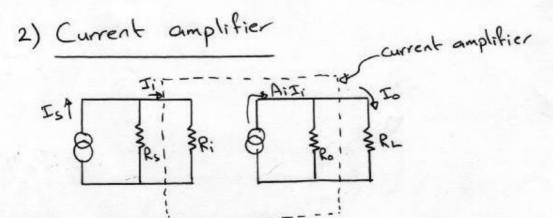

# Classification of amplifiers! - (Feed back) (Teed back) (Teed back)

R; >7Rs Ro <C RL

Ideally, R: = 00

.. Vo= Arvi = Ar Us

Uo = AV

the output voltage is proportional to the input voltage independently of RL and Rs.

Ri CCRs Ro >> RL

$$\frac{I_o}{I_s} = A_i$$

The output current is proportional to the input current and the proportionality constant is independent of RL and Rs.

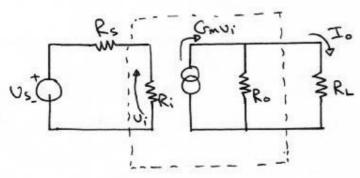

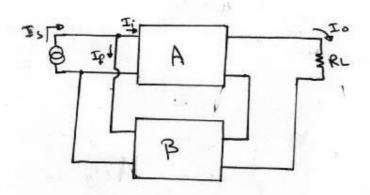

### 3) Transconductance amplifier:-

Gm is the transconductance of the amplifier

R.77 RL

R: >> Rs

Ideally Ri=00 Ro=00

Io = Cm vi = Gmvs

The output current is proportional to the input (3) Voltage independently of Rs and RL.

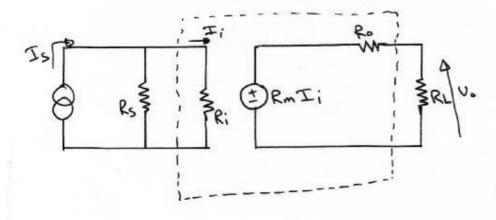

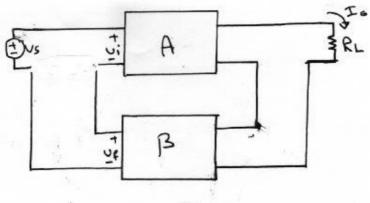

## (4) Transresistance amplifier:

Ri << Rs

Rock RL

Ideally: -

Ri=0

R. = 0

Uo= RmI; = Rm Is

15 = Rm

The output vollage is proportional to the input current independently of Rs and RL.

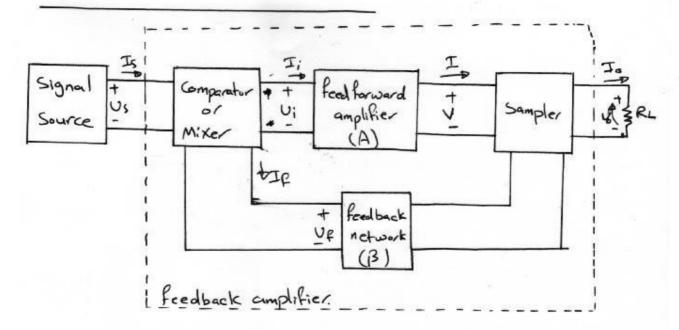

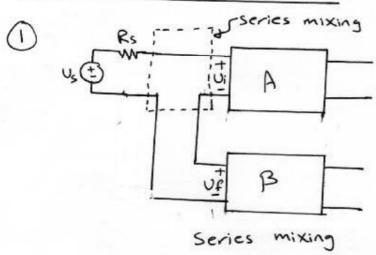

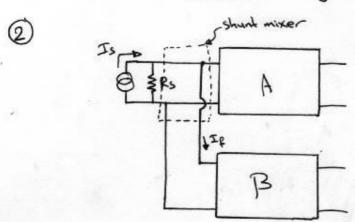

#### Mixers for Comparators

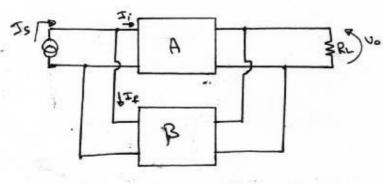

Shunt mixing

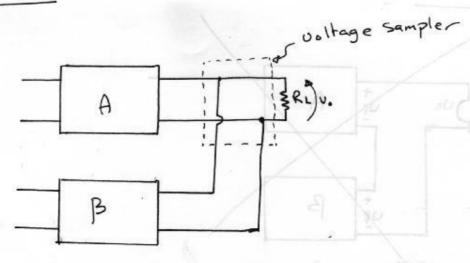

voltage sampling or node sampling

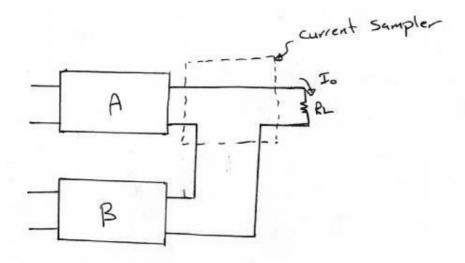

Current sampling or loop sampling

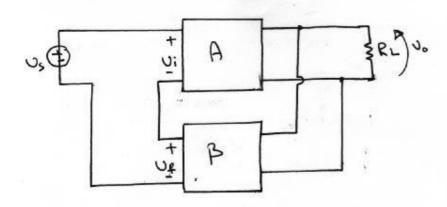

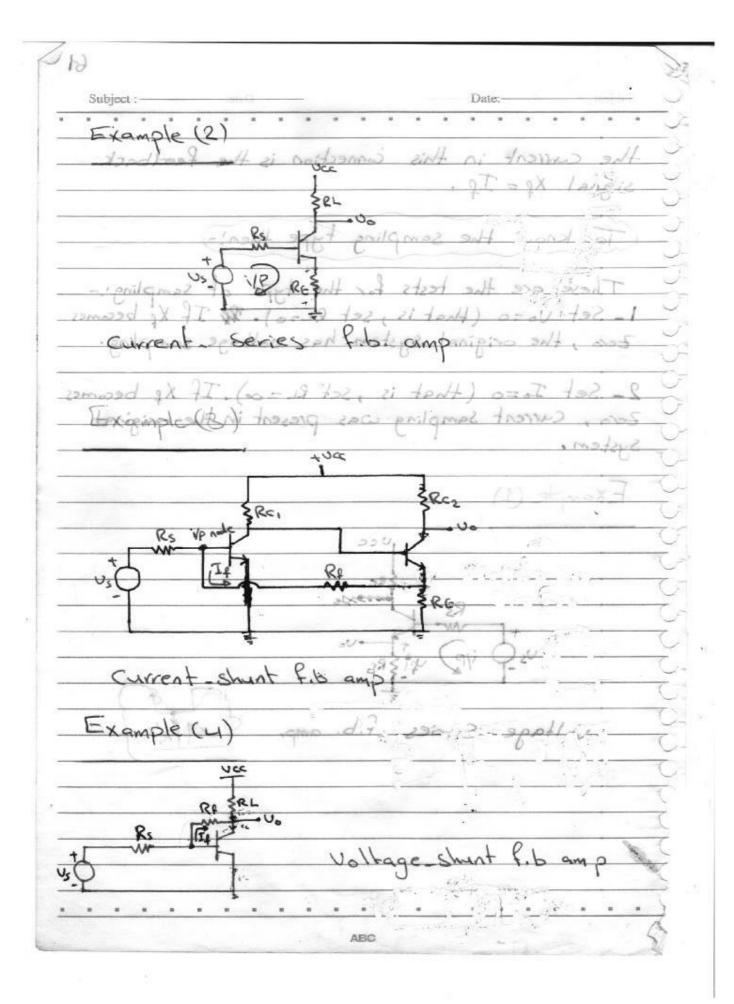

Voltage-Series feedback circuit.

Voltage-shunt f.b.

Current-Shunt P.b.

Current-series f.b.

#### Input Resistance: -

Rif > Ri for series mixing whether sampling is unltage or current.

Rif < Ri for shunt mixing whether sampling is voltage or current.

Input resistance:-

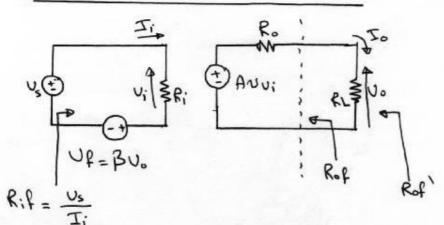

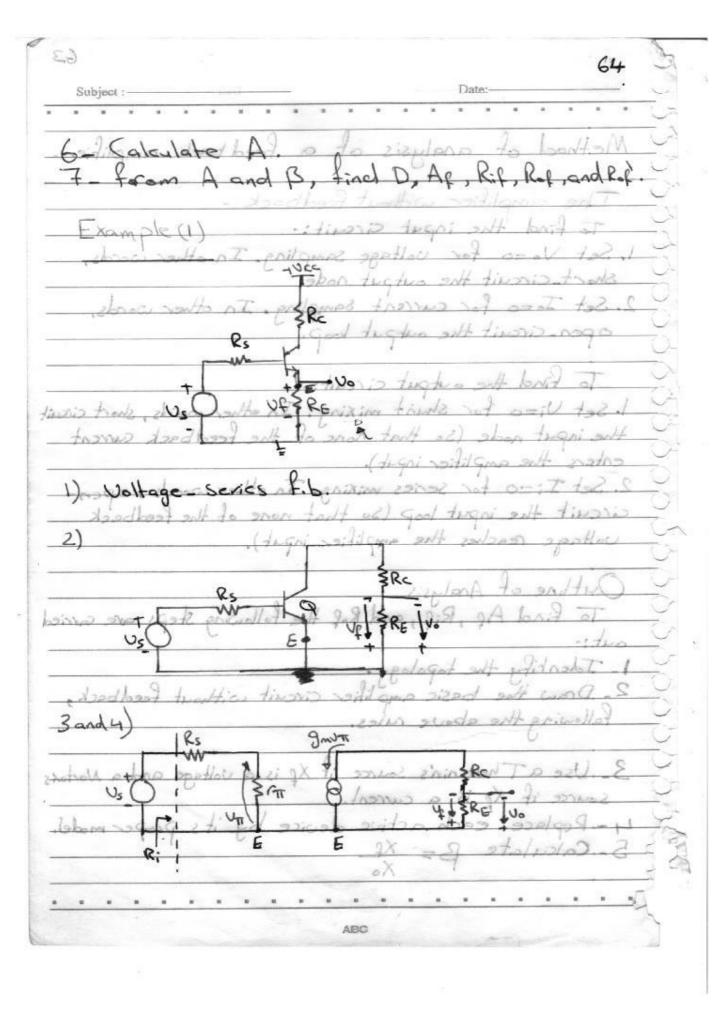

## 1 - Voltage - series feedback

Fig(a): voltage-series f.b. cct. used to find Rif, Rof, and Rof.

where

$$R_i f = R_i D$$

: R: 47 R:

Av is the open cct. voltage gain without f.b..

Av is the voltage gain without feedback but taking

RL into account.

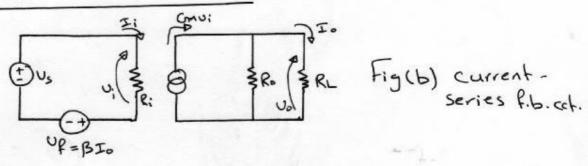

## 2- Current-Series f.b .: -

where

$$G_M = \frac{G_M R_o}{R_o + R_L} = \frac{I_o}{V_i}$$

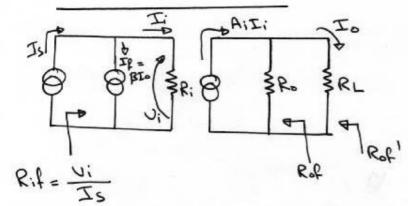

#### 3 - Current - Shunt P.b.: -

Figure (c):- Current-Shunt f.b. cct. used to calculate Rif, Rof and Rof'.

where

$$A_{I} = \frac{A_i R_o}{R_o + R_L}$$

$$R_i f = \frac{U_i}{T_s} = \frac{R_i}{1 + BA_{\perp}} = \frac{R_i}{D}$$

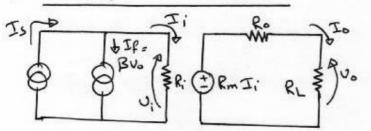

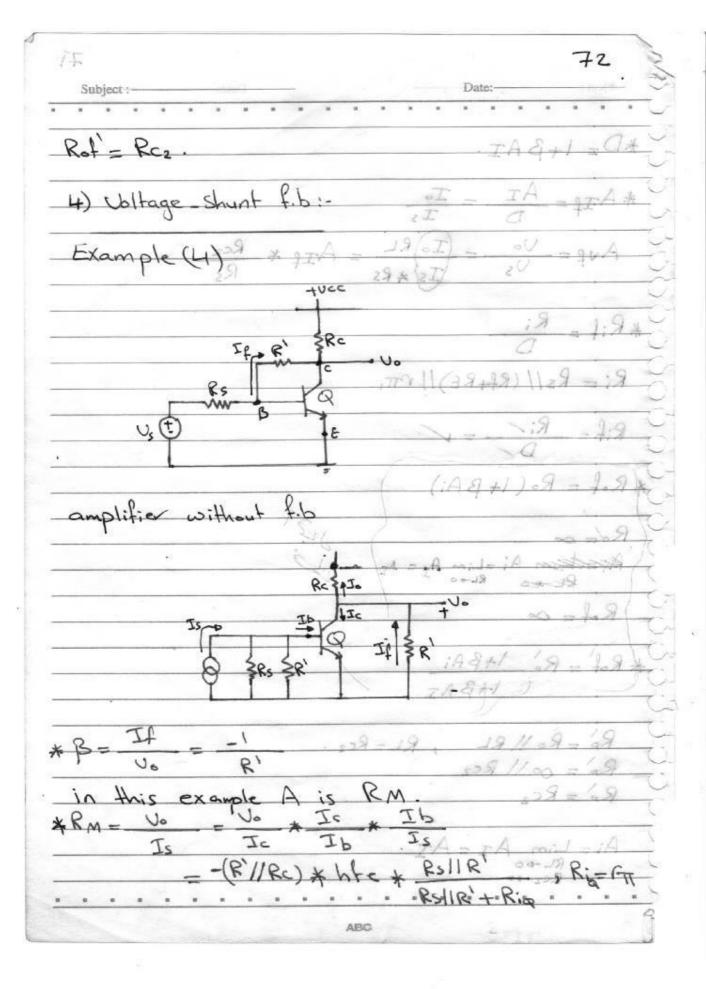

## 4 - Voltage - shunt f.b.:-

fig. (d) voltage-shunt f.b. circuit.

$$T_S = T_i + BRMT_i$$

$T_S = \frac{V_i}{R_i} (I+BRM)$

$$R_i f = \frac{R_i}{1 + BR_M} = \frac{R_i}{D}$$

: R, F < R;

Rm = Lim Rm RL-DO

#### Output resistance:

Rof < Ro for voltage Sampling

Rof > Ro for current Sampling

How to find the output resistance?

@ Open the olp cct. (disconnect RL) and impress a voltage source V instead which causes a current I to flow.

= where R= R11 RC

69 2 29

- (b) Set Us=0 for series mixing and Is=0 for shunt mixing.

- @ Find Rof = Y

- @ Find Rot' = Rof 11RL

1- Voltage series: Applying the above four steps to figure (a),

we find !-

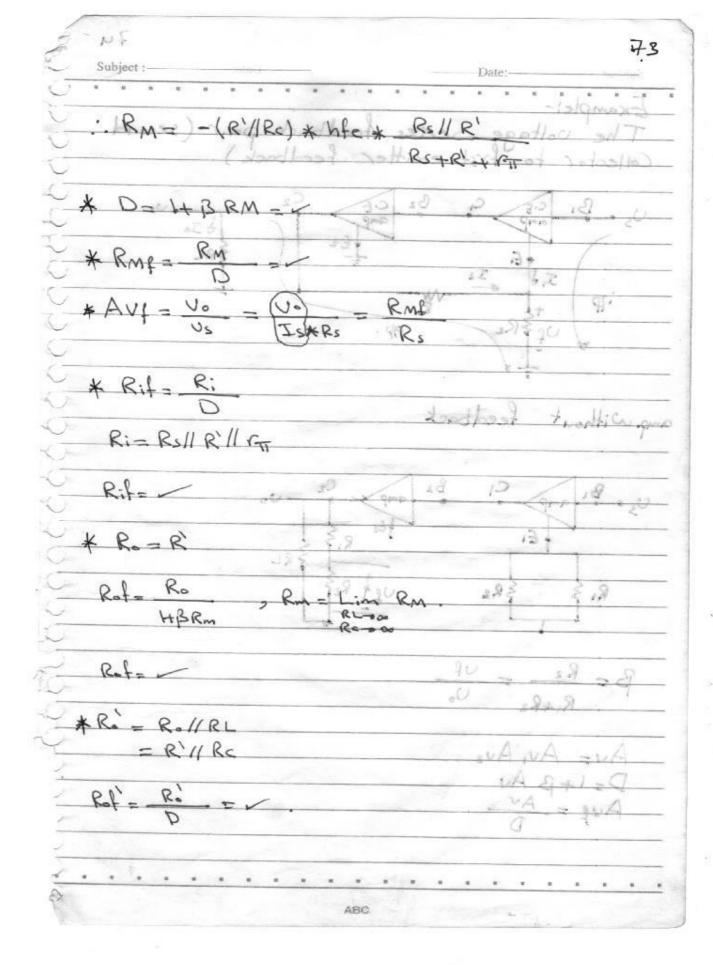

IM961 + IZ = 8 R.S' = R. = VI (HPRM) Rof'= Rò 19 = 19 = 1.9 17 = MARH = 19 where R' = R. 11 RL 19219: :. Rof <Ro Rof < Ro Rm = Lim Rm. Output resistancei-Rof CR. Par voltage sampling Ref 7 R. For current Sampling geonatrices tugtes out boil at wall @ Open the ofpect. (disconnect RL) and impress a voltage source V instead which couses a course I to Flow ( Set us so les series mixing and Is = o for - enixim trune V = 1.9 6,77 0 191129 = 29 Last D 1- Voltage series -Applying the above how steps to Figure (a). -! lovil sa 0+ (vA8+1)

$$R \circ \hat{F} = \frac{R'}{1 + \beta R m} = \frac{R'}{0}$$

Refer to fig(b) we obtain: -

Rot > Ro

Rof' > R'

: R.f > R.

## Specifying the topology: -

To know the topology we must first locate the ilp loop which is the mesh containing the applied signal Us and either

- (a) the base-to-emitter region of the first bipolar transistor, or

- (b) the gate-to-source region of the first FET in the amplifier or

(c) the section between the two inputs of a diff. amp.

Also the ip node which is (a) the base of the Pirst BJTor (b) the gate of the first FET or (C) the inverting terminal of a differential amp.

## (To know the mixing type as following:-)

The mixing is series if in the ip cct. there exist a circuit component & in series with us and if & is connected to the output (the portion of the system containing the load). If this condition is true, the voltage across & is the feedback signal Xf = Uf.

If the above is not satisfied, we must test for shunt mixing. The mixing is shunt if there is a connection between the i/p node and the o/p circuit. The current in this connection is the feed back signal XF = If.

## STO know the sampling type then:

These are the tests for the type of sampling: -

- 1. Set Uo=0 (that is, set RL=0). If Xf becomes Zero, the original system has voltage sampling.

- 2. Set Io=0 (that is, set RL=00). If Xp becomes Zero, current sampling was present in the original system.

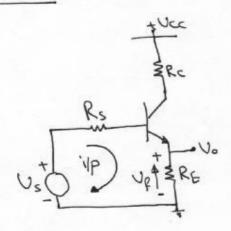

#### Example (1)

Voltage-series f.b. amp.

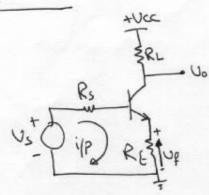

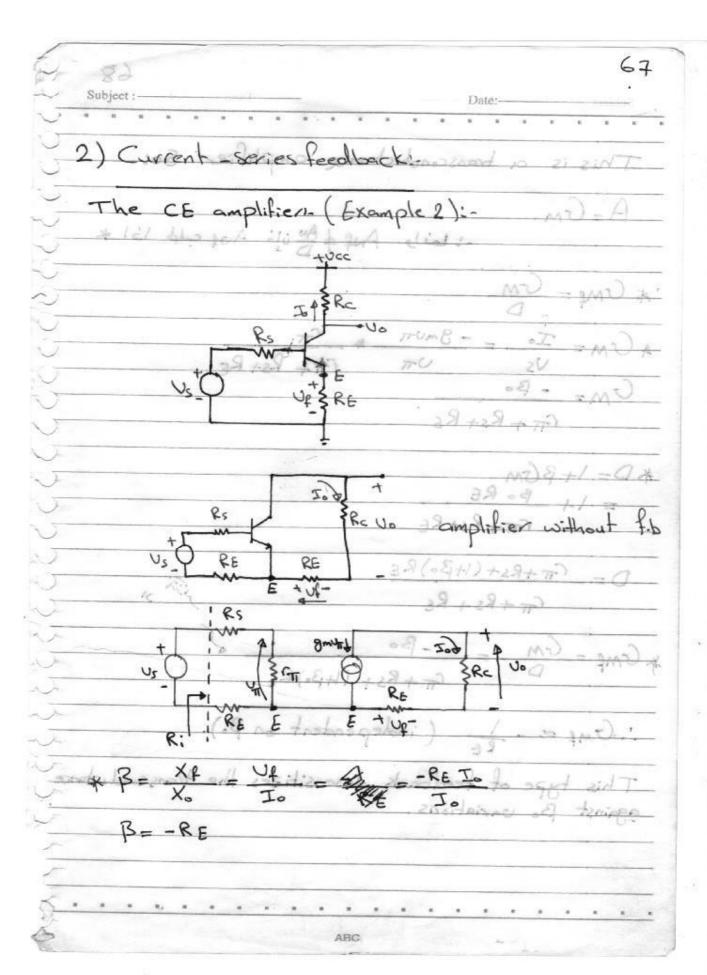

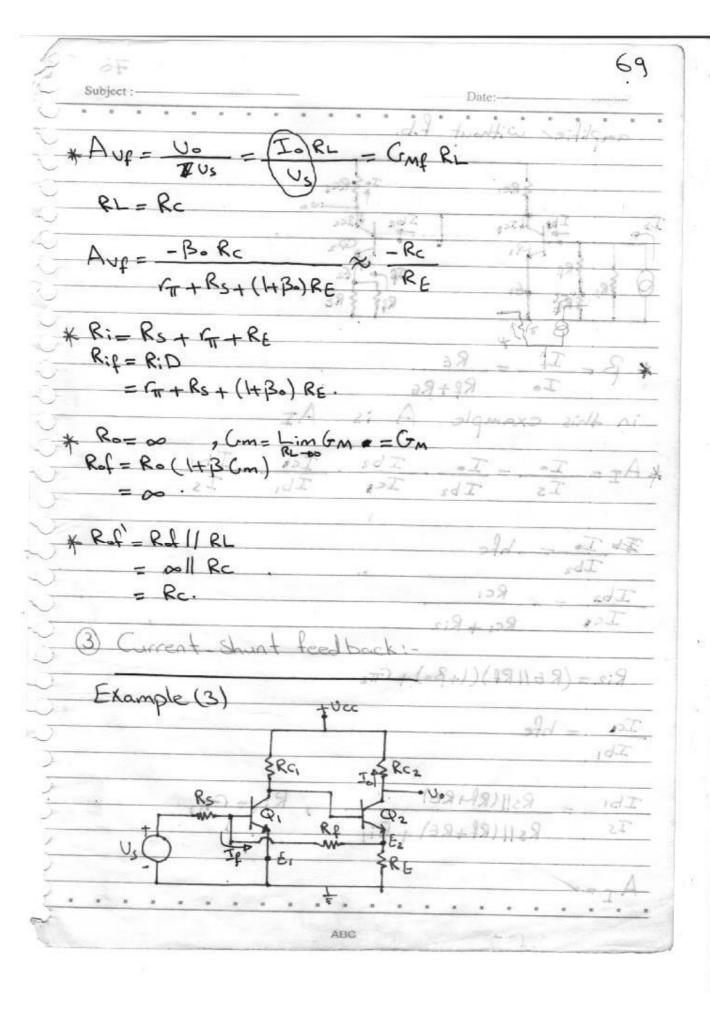

#### Example (2)

Current - Series P.b. amp.

Date:-

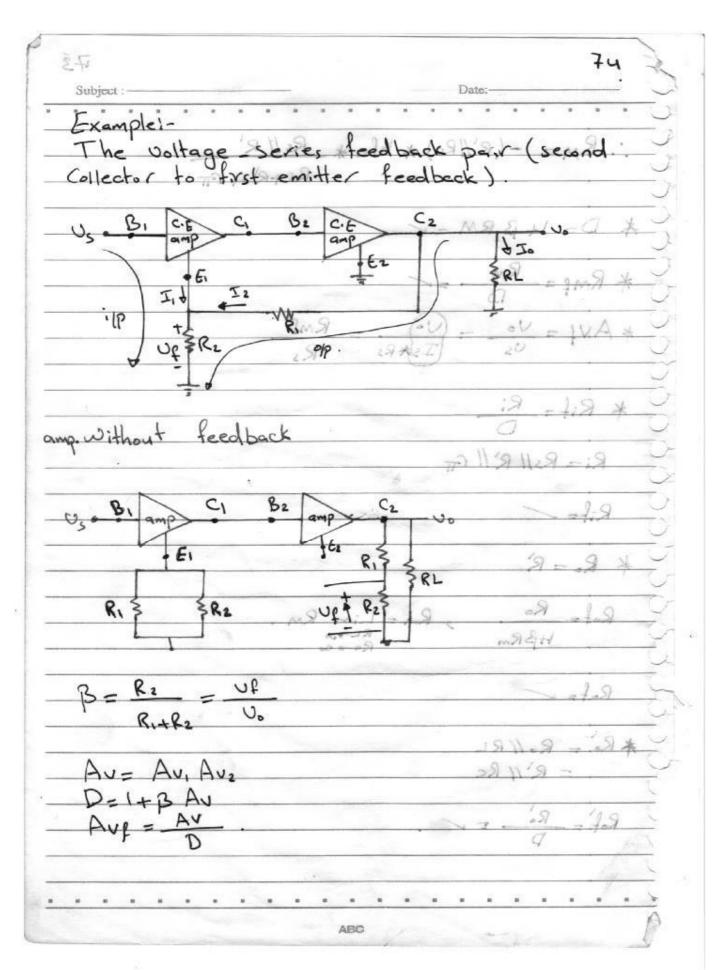

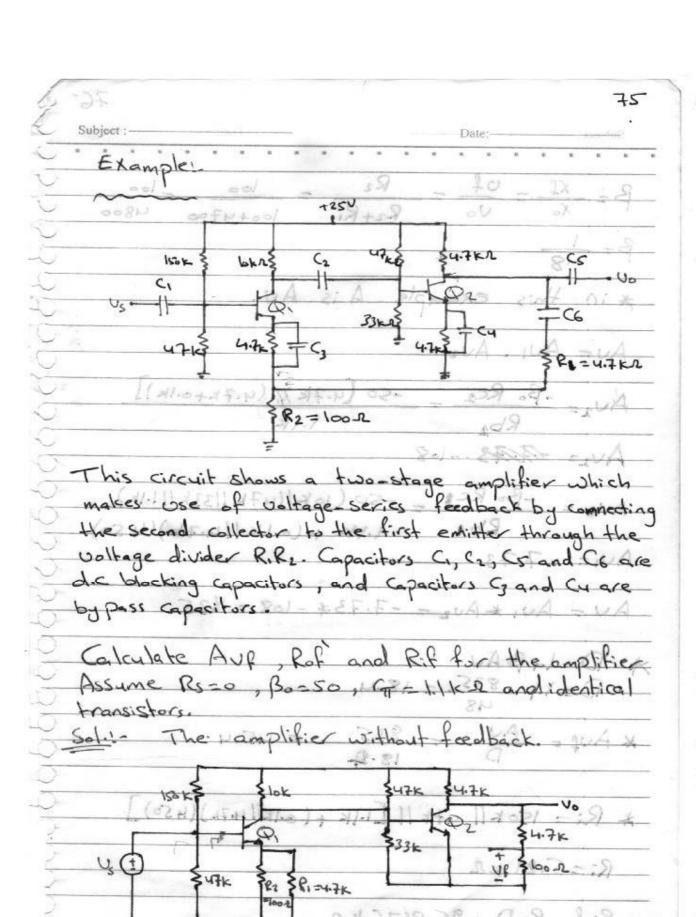

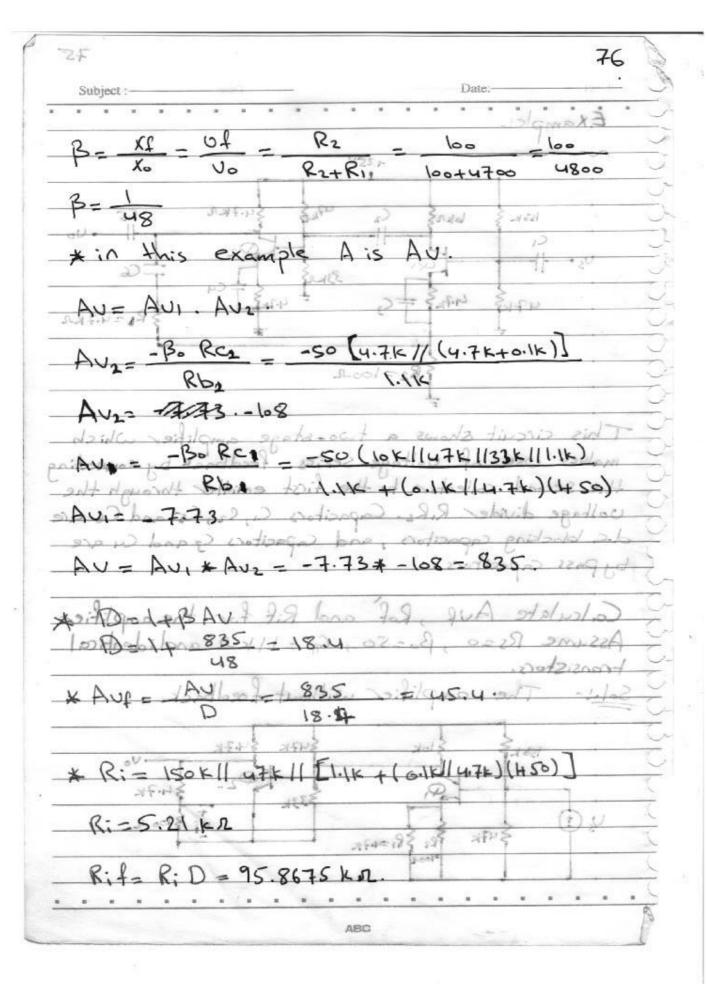

in this example A is Au

AV= Vo - 9m Vm RE G BORE

7) find D. Af, Rif, Rof, and Rof.

D= 1+BAU

= 1+ BORE = FATRS+BORE

Auf = Au = Bo RE rtt + Rs + BoRE

for (Bole) >> = +Rs

Aug 21

This type of feedback desensitizes the voltage gain against Bo variations.

R:= F# + Rs R:E = R: D

Rif = CT + RS + BORE.

66 65 R. 1+BAV AV=Lim A RL = RES + AN=00 = Roll RL = 00 11 RE - RE Rf' = (r+ Rs) RE ( + RS + BORE Rof' - Roflike m+Rs transmission through the B-network. In the Co amplifier forward current ( the ba is not the case since current) also flows through RG. Therefore the expressions for Rot and Rif have (Bott) replaced by Boo

29

Subject:

This is a transconductance amplifier So:

A=Gm.

+ Ich Als to And of And clas 191 \*

\* CM= GM

+ CM = IO = - 9mUTI THE RS+ RE

CM = - 150

\* D= 1+ BGM = 1+ BORE

THE PSTRE OU

D= (T+Rs+(HBO)RE

CTT+RS+ RE

\* GMF = GM = 6-2-B0 1430) RE

: Gmf = - RE (independent on B.).

This type of feedback desensitizes the transconductance against Bo variations.

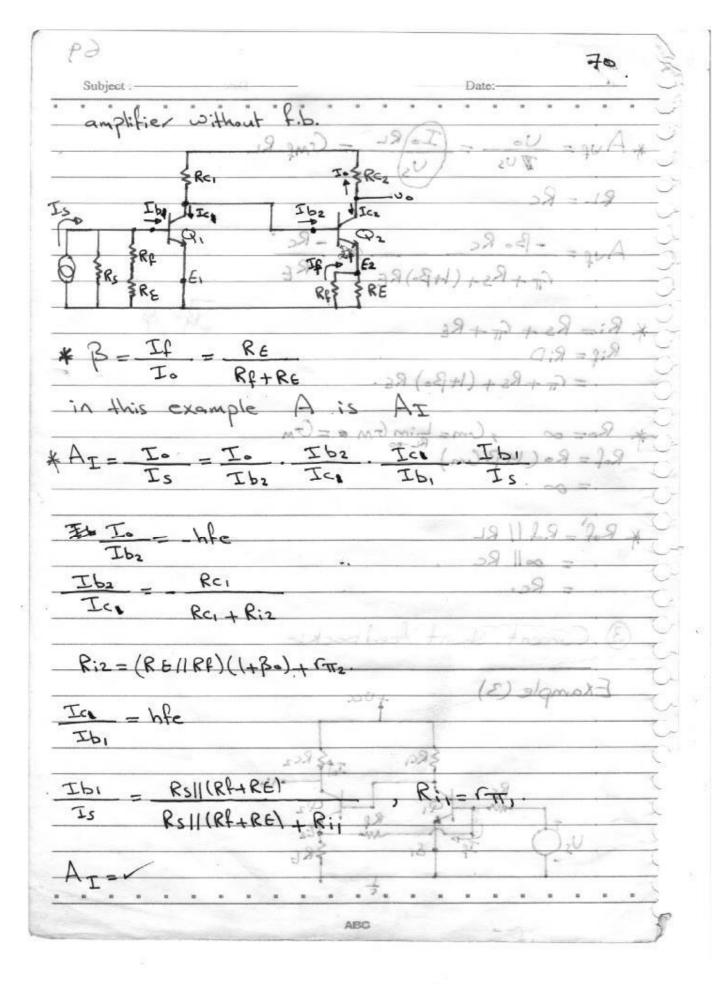

SF Subject:-

Date:

71

\*D= 1+3AT

\*AIf = AI - I

Auf = Vo ToRL = AIf \* Rcz Rs

\*Rit = R;

Ri = Rs//(Rf+RE)//rTT,

R:f = R: - - V

\* Rof = Ro (1+ BA:)

Ro= 00

Ai = Lim Az = Az

Rof = 00

\* Rot' = Ro' 1+BA: 1+BAI

Ro = Ro 1/ RL , RL = Rc2

Ro = 00 11 Rcz

Ra = Rcz

Ai = Lim AI = AI

| r-t-                                                    |                   | 80        |

|---------------------------------------------------------|-------------------|-----------|

| Subject:                                                | Date:             |           |

|                                                         |                   |           |

| The Barkhausen criterian f                              | or oscillati      | odeisa.   |

| The Barkhausen criterian f<br>- 1 A(jwo) B(jwo) = 1 (e) | A(2)8-1           |           |

|                                                         |                   |           |

| Alian Blive                                             | solo A las        | nog ni    |

| By this ise have - por                                  | no shoog          | ab (2) of |

|                                                         |                   | elements  |

| AB-1                                                    | ci nipe 9         | sol soll. |

| $X_0 = AX_i$                                            |                   |           |

| Xt = Bx : noise/12                                      | Oscillation       | Q.The     |

| 1- XT = ABX God, AB= Insuport                           | al socation       | to 27     |

|                                                         |                   | . 1327    |

| .   Xq = Xi (no input).                                 | 0 = A             | 8-1.      |

| \(\frac{1}{1}\)                                         | 000 0             | jA bos    |

|                                                         |                   |           |

| chape a finite a start to Esta                          | 6 toot 200        | This me   |

| definition on noting                                    | td 21 dain        | a fugni   |

| X B                                                     |                   | 0         |

| Control of the Satelliago THEN                          | 2 314 33          | 1:        |

| ABI 5% genter than unit;                                | · La stack        | and       |

| maintain Oscillation                                    |                   | w)A\      |

| maintain Oscillation i                                  | 6 12 (            | 0         |

|                                                         |                   |           |

|                                                         |                   |           |

|                                                         |                   |           |

|                                                         |                   | 1000      |

|                                                         | A THEY BY THE PEN |           |

82

Date:

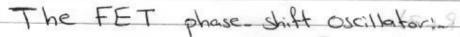

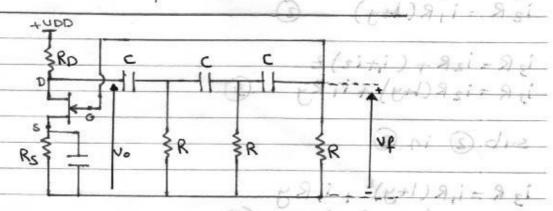

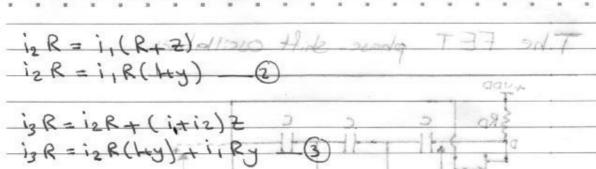

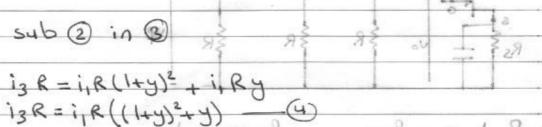

To find the frequency of Oscillation:

- @ find B(jw) = ? B= of

- @ Set the imaginary part = and derive fosc.

so for this circuit we have ( ( )) 9;

let Z Jwe and y = Z and X = wcr

Date:-

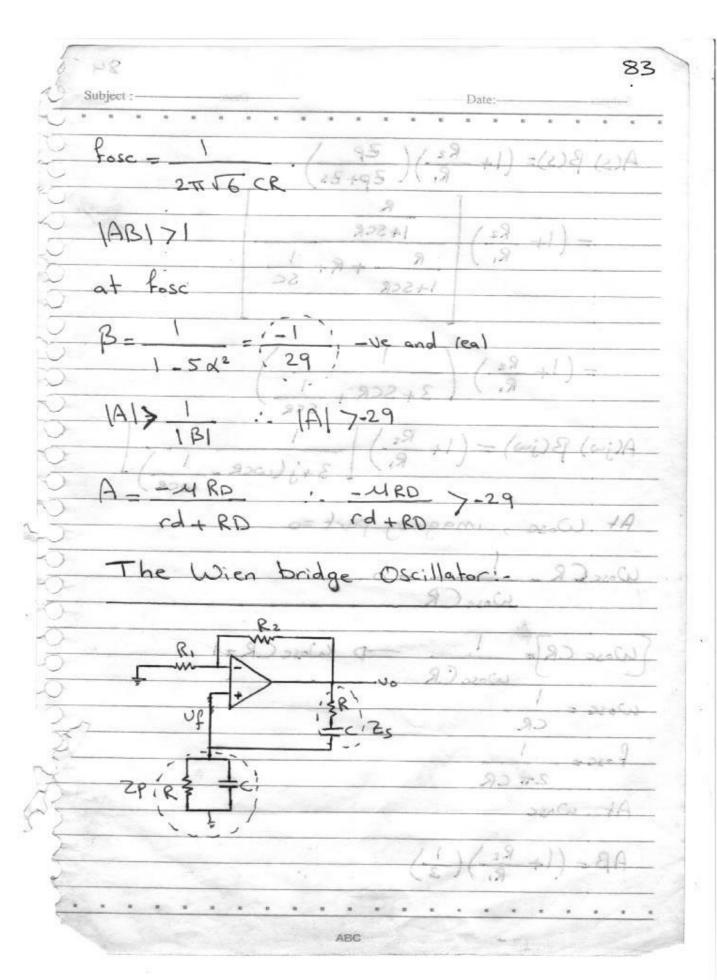

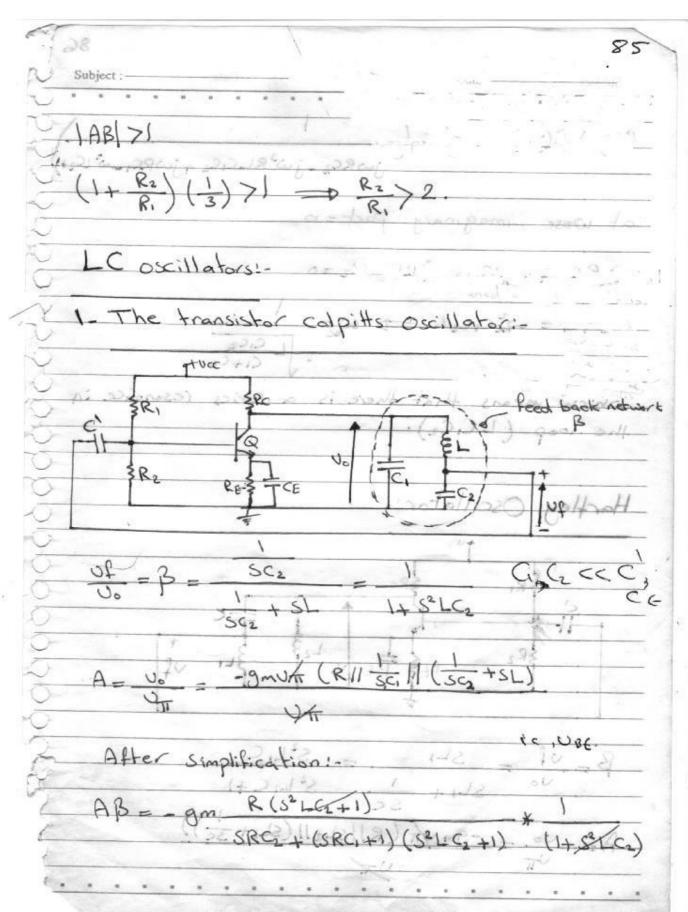

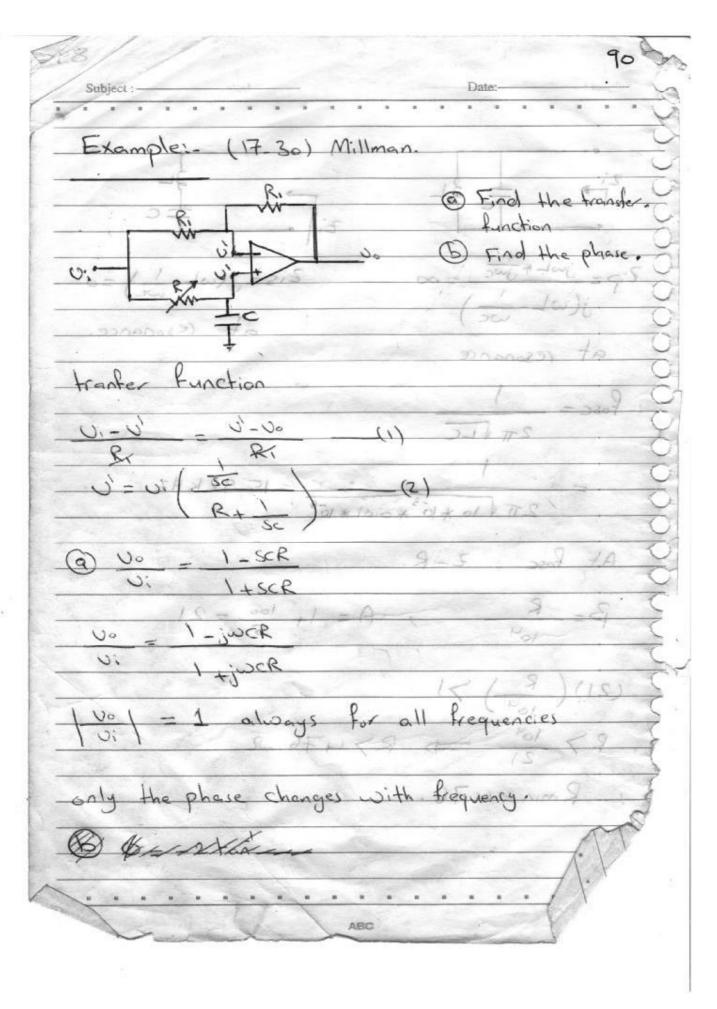

83 84 Date: Subject:-R2 \ 1+SCR SC 1+SCR WCR WoscCR Wose CR Wose CR 2TT CR stout. At Wosc 4928 ABC

Subject:

Dates

#### B = - 2 tan wer

If R is varied as C remains constant, this configuration acts as a constant-amplitude phase shifter.

If R=0, \$=0 If R=00, \$=-180 or 180

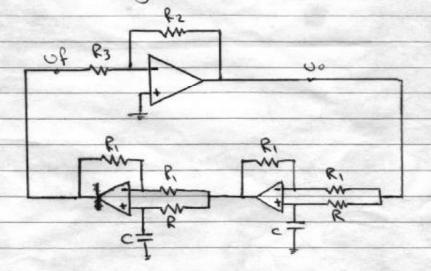

Tf two phase shifters are cascaded and the loop is completed with an inverting op-amp then this system will oscillate at a frequency force as following:

\$ = total phase shift of the B-network only

OT = - 4 tan wer

Фт = -180 at fosc.

## Multivibrators

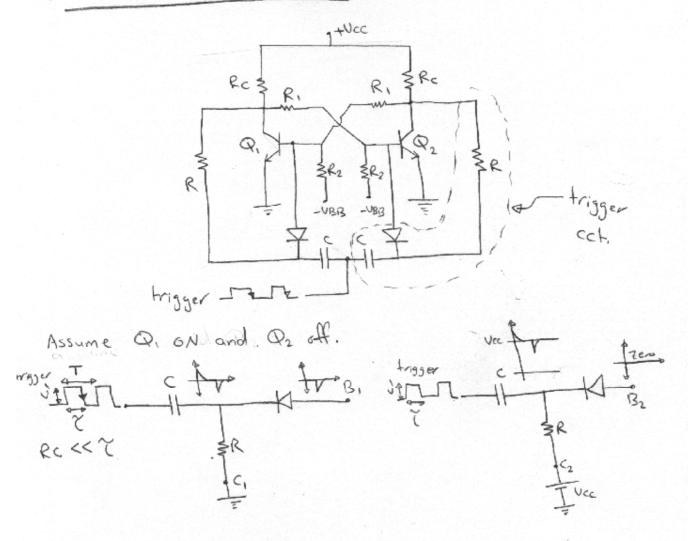

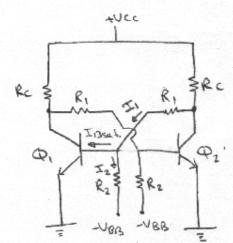

## 1) Bistable Multivibrators:

The Bistable multivilbrator has two stable states :-

Owhen Q ON, Oz off.

Dwhen Q, off, Q2 ON.

In order to design this circuit, assume on of the transistors are on and the other off, so let Q on and Q2 off.

$$T_1 = \frac{Ucc - UBE}{Rc + R_1} = \frac{UBB + UBE}{R_2} + TBset. - (1)$$

IBsat. > IBmin (In order for the transistor of to be well interturation)

assume IBsat. = 2 \* IBmin.

$$V_{B_2} = 0.2 * \frac{R_2}{R_1 + R_2} + (-V_{BB}) \frac{R_1}{R_1 + R_2}$$

(2)

Assume UB2 =- 1 (In order for Oz to be off).

$$-1 = 0.2 * \frac{R_2}{R_1 + R_2} + (-VBB) \frac{R_1}{R_1 + R_2}$$

This multivibrator is designed such that one transistor is well into Saturation and the other is well below cut off.

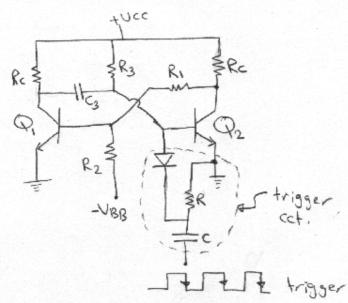

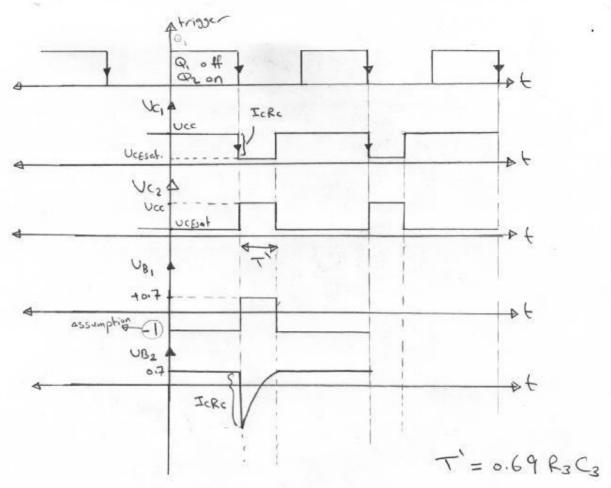

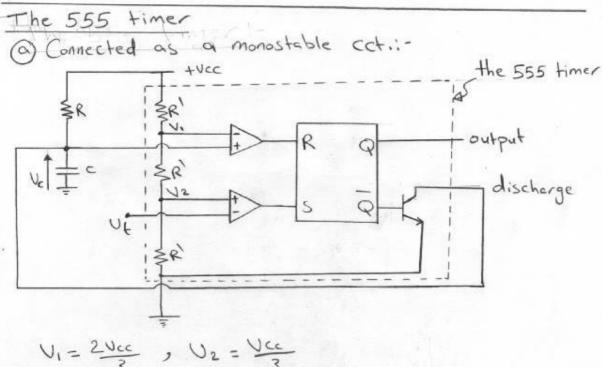

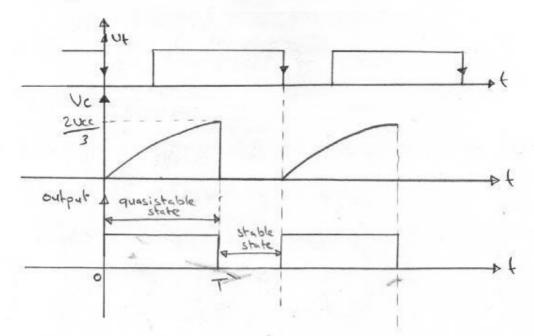

### 2 Monostable Multivibrator:

The monostable multivibrator has one stable and one quasistable state, they happen when "-

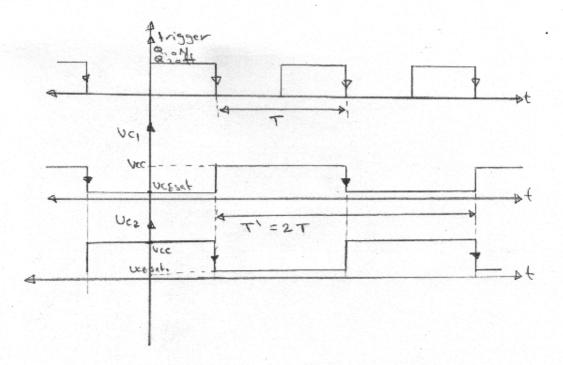

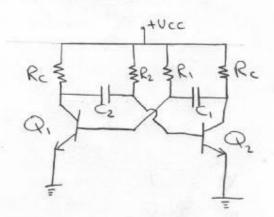

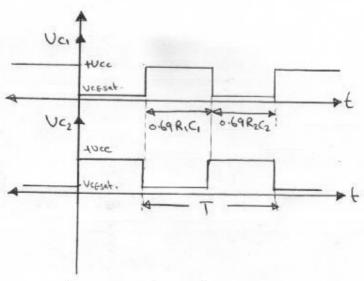

## 3 Astable Multivibratori-

This multivibrator has no stable states. The circuit operates as a free running oscillator without external trigger.

T= period of the pulse train.

T= 0.69 RIC1 + 0.69 R2C2

if RI=RZ=R and CI=CZ=C

then we have a square waveform generator with a

period T= 1.38 RC.

Uti- trigger

Uty Vcc

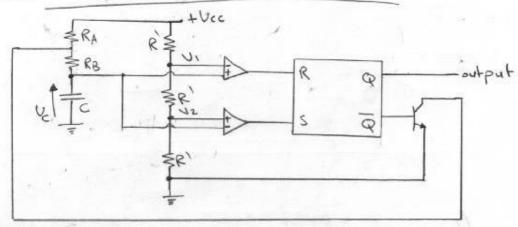

(b) Connected as an astable cct. :-

# Digital-to- Analog (DIA) converters !-

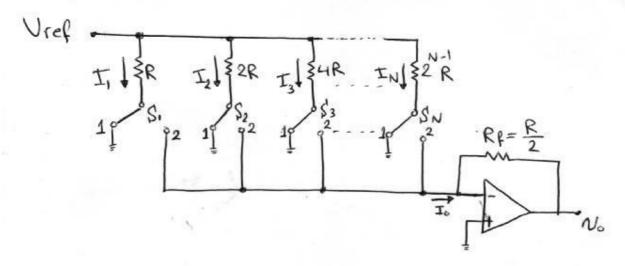

## 1) Binary-weighted Resistor DIA Converter:

An N-bit DIA converter using binary weighted resistors

- \* The Switches are controlled by an N-bit digital input: (bi, b2, ---, bN).

- \* bi is either 0 or 1.

- \* by is the least significant bit (LSB) and by is the Most # (MSB).

$$D = \frac{b_1}{2'} + \frac{b_2}{2^2} + \frac{b_3}{2^3} + - - + \frac{b_N}{2^N}$$

so that the output No is directly proportional to the digital input signal.

\* a disadvantage of Binary weighted Resistor DIA converter is that when N74 there will be a difficulty in maintaining accuracy of resistor values.

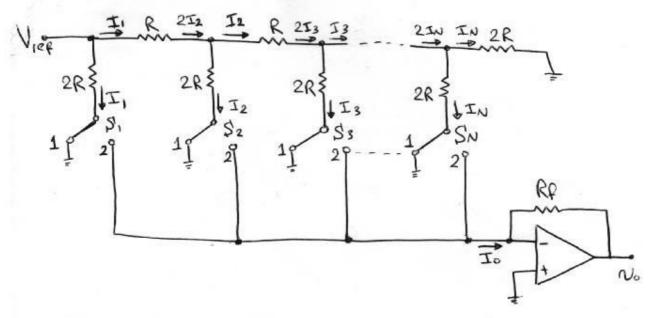

### 2) The R-2R Ladder BIA

6

$$I_1 = 2I_2 = 4I_3 = - - = 2I_N$$

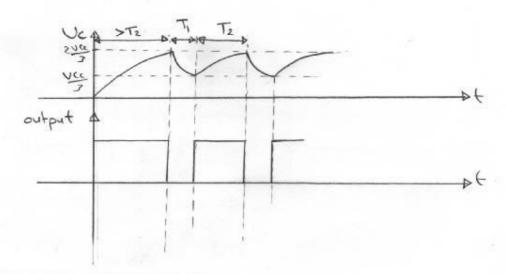

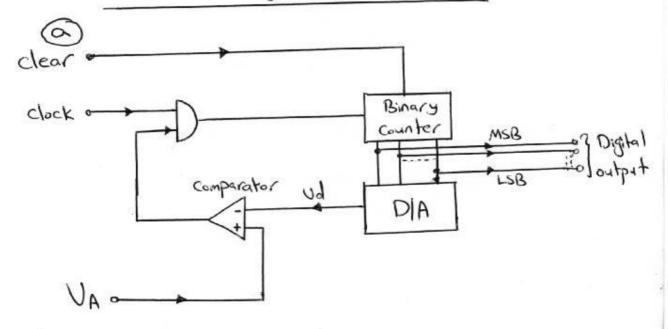

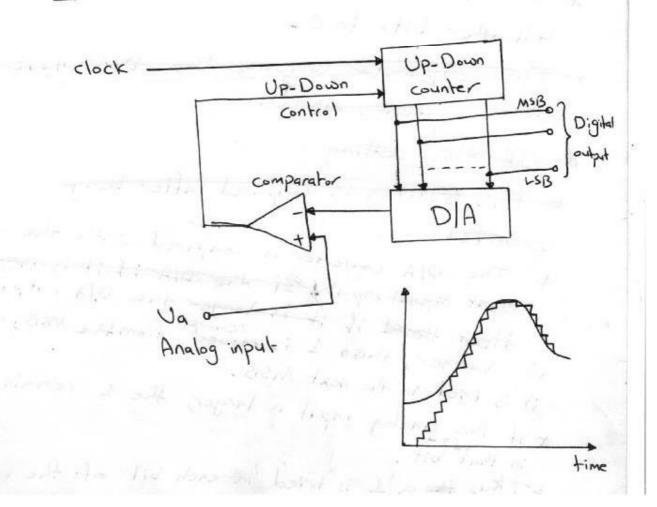

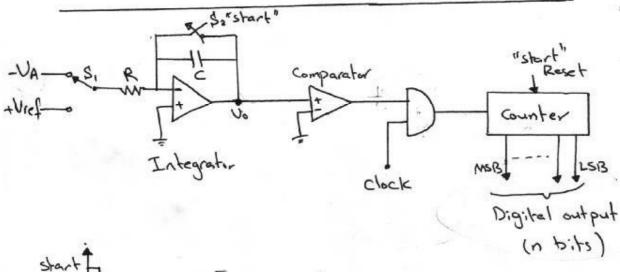

The Counting AID converter !-

Analog input

\* The clear pulse resets the counter.

\* The counter will then count the number of clock pulses.

\* This count will be converted into Analog by (DIA).

\* If this count is still less than Ua the counter continues untill the counter reaches the value of UA.

\* At that point the AND gate is disapled and the counting stops.

\* The counter reading represents the analog input

\* If Ja is varying with time then a sample and hold circuit is required. The minimum interval between samples is to be nT seconds, where look a number of pulses for the maximum n = is the number of pulses for the maximum value of the analog voltage.

T = is the clock period.

(B) Tracking or Servo counting AID converter:

The Conversion time is small for small changes in the sampled analog signal and hence this system can be used effectively as a tracking AID converter.

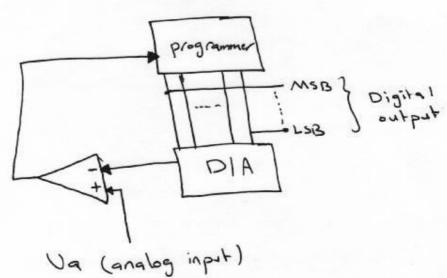

### 2) The Successive - Approximation A 1.D Converter

\* The programmer sets the MSB to 1 with all other bits to 0.

\* The DIA converter output is compared with the analog input, if the DIA output is larger, the analog input, if the DIA output is larger, the I is removed from the MSB, and it is tried in the next MSB.

\* if the analog input is larger, the I remains in

\* Thus a 1 is tried in each bit of the DIA

Converter until the binary equivalent of the analog

Signal is obtained at the end of the process.

\* For an N-bit system, the conversion time is N clock periods as opposed to a worst case of 2" clock periods for the counting-type AID converter.

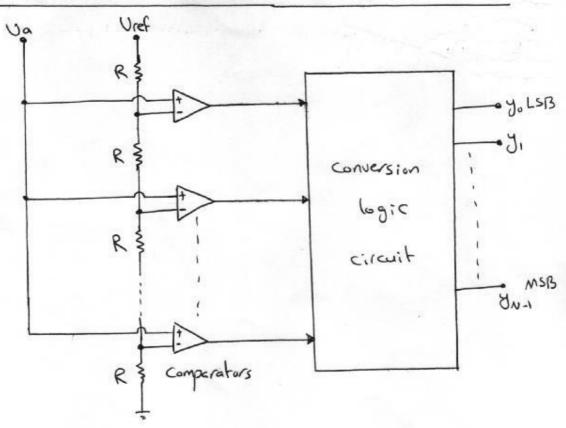

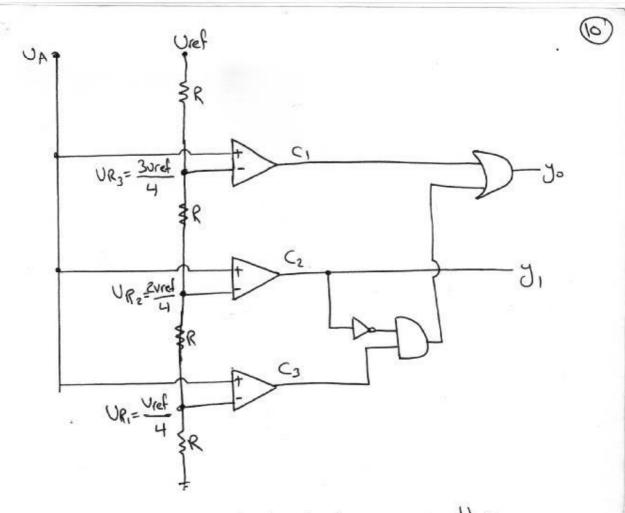

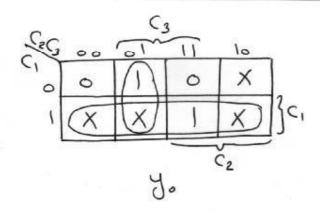

3 The Simultaneous, parallel or Flash AID converter s-

This converter is the fastest of all converters.

for example if N=2 then 3 comparators are required where Va is applied to them simultaneously and compared with equally spaced thresholds as in the following:

\* a disadvantage of this technique is the complexity of hardware. The number of comparators needed is 2-1 where N is number of output bits.

| Va                 | $C_3$ | $C_2$ | C, | - 4, 4. |

|--------------------|-------|-------|----|---------|

| a War Viel         | ٥     | 0     | 0  | 0 0     |

| o < Va < Viet Viet | ١     | 0     | 0  | 0 1     |

| zviet < Va < 3viet | 1     | ١     | 0  | 10      |

| 3 vret < Va < Vret | ١     | ١     | 1  | 1 1     |

| ч                  |       |       |    |         |

| 7                  |       |       |    |         |

$$y_1 = C_2$$

$$y_0 = C_1 + C_3 \overline{C_2}$$

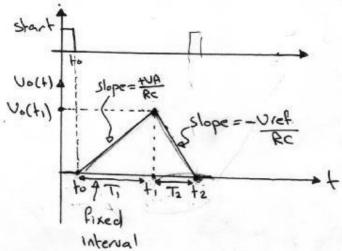

## @ Integrating Dual-Slope AID converter:

This converter is very accurate but very slow.

### Logic families

### Logic circuit characterization: -

The following parameters are used to characterize the operation and performance of a logic -circuit family.

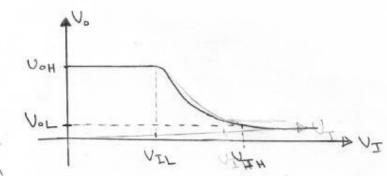

@ Noise Margins :-

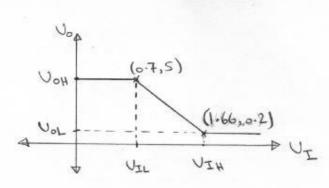

Typical voltage transfer cle's (UTC) of a logic inverter

\* The UIL is the maximum value that the input can have while being interpreted by the inverter as representing a logic (o).

\* The VIH is the maximum value that VI can have while being interpreted by the inverter as representing lagic (1).

for example:

NOT AIT

NMH = VOH - VIH NML = VIL - VOL \* The robustness of the logic cct. family is defined by its ability to reject noise and thus by its noise margins (NMH, NML).

(b) power dissipation

There are two types of power in alogic gate, static and Dynamic.

static power dissipation & is the power the gate dissipate in the absence of switching action. It results from the presence of a path between the power supply and ground in one or both of its two state. (i.e. with the olp either low or high).

Dynamic power dissipations-Occures only when the gate is switched due to the presence of a capacitor between the olp node and ground.

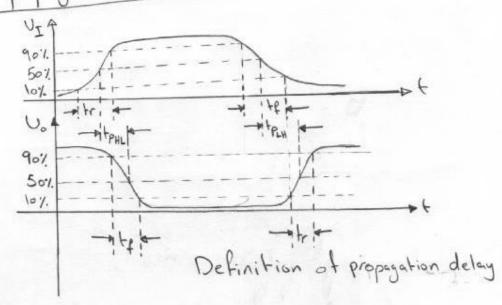

Opropagation delay:

tr: the rise time.

tp:- the fall time.

EDIL :- High-to-Low propagation de

EPHL: High-to-Low propagation delay. EPLH: Low-to-High propagation delay.

### 1 Fan out:

The fan out is the maximum number of similar gates that a gate can drive while remaining within gavanteed.

Specifications.

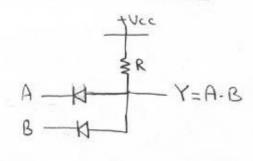

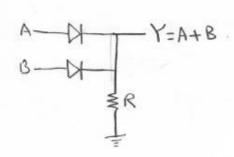

### 1 Diode Logic family

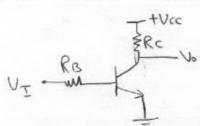

### The BJT Digital Circuits:

Basic BJT Inverter:

### Example :-

Draw the VTC of the basic BJT inverter if RB = 10KIR, Rc = 11KIR, BF = 50 and Vcc = 5V.

Solytion:

- 1) if the ip equals a low voltage  $V_I = V_{0L} = V_{0} = 0.2V = V_{0} = 0.2V$ .  $V_{0} = V_{0H} = V_{0C} = 5V$ .

- ② At UI = UIL, the transistor begins to turn on, then UIL = 0.7 U.

- 3) if  $V_{IL} < V_{IH}$ the transistor is in the active region having again of  $Av = \frac{-\beta_0 Rc}{RB + VH}$

- I I Bmin = I csat.

BF

I csat. = Ucc Ucesat.

Re

VIH = IBmin \* RB + 0.7 => from the i/p loop.

- - IBsat. = UoH-o.7

6 NMH = VOH - VIH = 3,340 NML = VIL - VOL = 0.5 V.

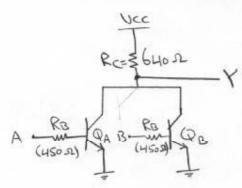

### Resistor Transistor Logic (RTL)

A two input NOR gate of the RTL family

Y= A-B = A+B

\* The noise margins of the RTL gate are narrow because the VoH is lowered when driving other similar gates. \* The RTL gate dissipate a large amount of power (12 mw).

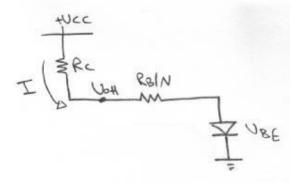

Example: - An RTL gate is driving N similar gates, find an expression for VoH in terms of N and then find the value of VOH , if N=5.

#### Solution :

VoH = Vcc - Rc Vc-VBE Rc+ RB

if Ucc=3v , N=5

V6H = 1V

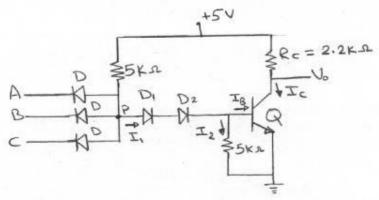

### Diade Transistor Logic (DTL) family:-

DTL NAND gate

### Example:

For the DTL NAND gate above, assume that UBEST, U6 = 0.5 V, and Ucesch. = 0.2 V. The drop across a conducting diode is 0.7 V and U6(diode) = 0.6 V (A) Verify that the Cct. functions as a NAND gate for BF > BFMin (assume that Q is unloaded by a following gate).

- (B) Calculate BEmin.

- @ Will the circuit operate properly if Dz is not used. Solution:-

logic (o) = Ucesat = 0.2V. logic (1) = Ucc = 50.

\* if at least one input is low its diode conducts and Up=0.2+0.7=0.9 V. Di and Dz are not conducting Since 3\*0.7 = 24 U is required and UBE = OV. Since Ux of Q=0.54 Her Q is off :-

1. Y= Vcc = 5v = logic (1).

\* Now, if all inputs are high at U(1) = Vcc=5v. Assume all input diodes are off, that Drand De conduct and that Q is in saturation.

So Up=0.7+0.7+0.7=2.1V.

then each input diode (O) will have a voltage of 2.1v on its anode and SV on its cathode, thus justifying the assumption that Dis off.

$T_1 = \frac{5-2.1}{5K} = 0.58 \text{ mA}.$

I2 = 0.7 = 0.14MA.

IB = I1-I2 = 0,44 MA.

Assuming that BF > BFmin , this value of IB.

Saturates Q and makes  $V_{i} = V(0) = V(0) = V(0) = V(0)$ Shave verified the NAND gate.

B

$$T_{cset} = \frac{5 - 0.2}{2.2} = 2.182 \text{ mA}.$$

Bf min =  $\frac{T_{cset}}{T_B} = \frac{2.182}{0.44} = 4.96$

Thus for BF7 4.96, the assumption of Q is Saturated is valid.

© If at least one input is at U(0), then Up=

0.2+0.7=0.9V. Hence if only one diode Dis

Used between p and the base B, then UBF=0.9-0.6=

0.3V, where 0.6V is the diode cut-in Voltage. Since

the transistor cut-in Voltage is U-6=0.5U, theoretically

the transistor cut-in Voltage is not a very conservative

Q is cut-off. However, this is not a very conservative

design because a Small (70.2V) Spike of noise

will turn on.

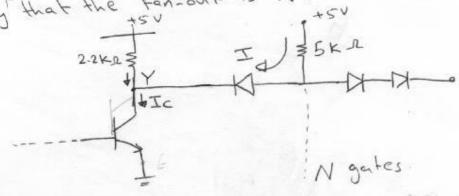

If the DTL gate is driving N similar gates, we say that the fan-out is N:-

when Y= V(0) = 0.2 v, the input current I. of a following stage adds to the collector current of Q.

Assume all the inputs to the diodes of the following stages are high except the ones driven by Q.

then

$$T = \frac{5-0.9}{5} = 0.82 \text{ mA}$$

.

total Icof q = 0.82. N + 2.182 mA.

IB the same as before loading = 0.44mA and assume a reasonable value of Bmin = 30

Ic= BEmin IB

Tc = 0.82 N + 2.182 = 30 \* 0.44 = 13.2 mA.

N=13.436, N must be an integer than N=13. of Course the current rating of Q must not be exceeded.

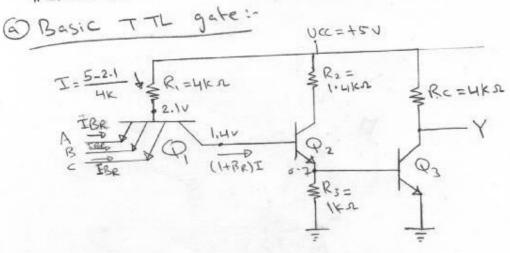

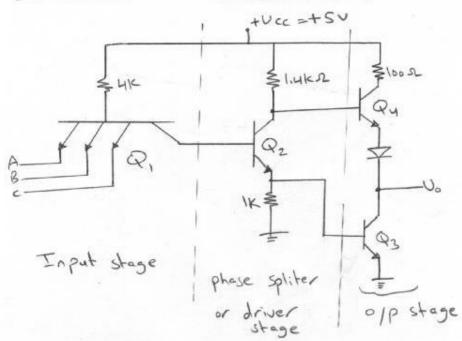

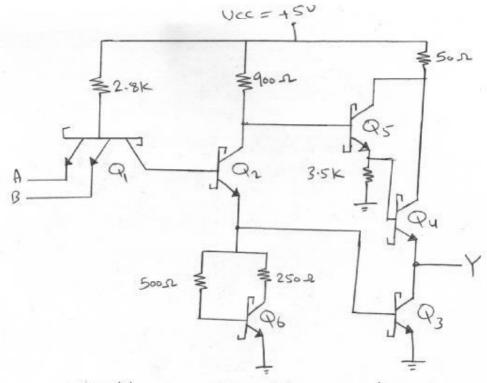

Transistor - Transistor Logic (TTLaTZL):0-

TTL - NAND gate (when all inputs are high)

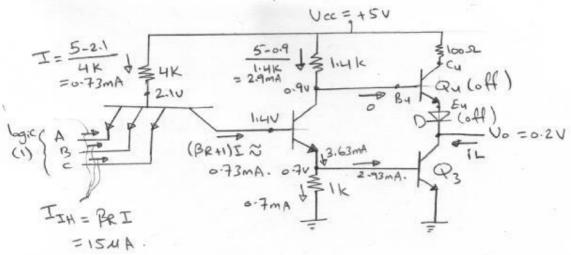

(ase I: - when all inputs are high = logic(1)

\* The emitters of Q, are reverse biased.

\* The Collector/ Base junction of Q, is forward biased.

\* Q, is operating in the inverted active mode.

\*BR (reverse B) is very small. (BR=0.2)

\* (BR+1) I is a sufficient current to drive Q2 and Q3 into saturation and the output Y equals to logic (o) = 0.20.

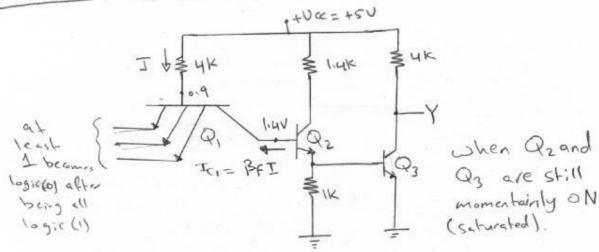

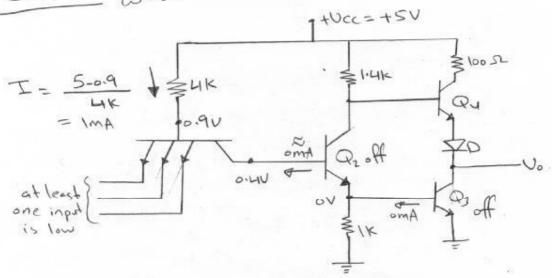

Case I :- If at least one of the inputs is U(0).

\* The current I will be diverted to the emitters of

\* The baselemitter junction of Q, is forward biased. Q.

\* UB of Q, = 0.9V. momentainly

\* Q, is operating I'm the normal active mode:

\* Ici = BfI which is a large current that will turn Q2 and Q3 off.

\* when Q2 is off IB2 is a small current (in nanocmperes), so IB, 7 ICI and Q, will saturate.

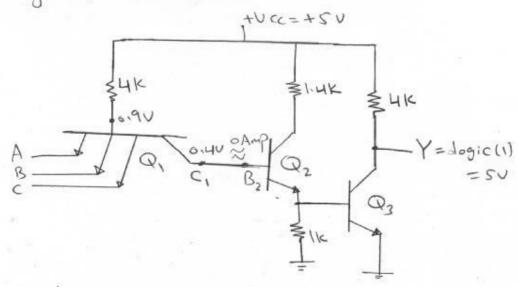

\* Uc, equals 0.2 to.2 = 0.40, which is a small voltage that will keep Qz and Q3 off.

Y = logic (1) = V = 5 V-

when Q2 and Q3 are off.

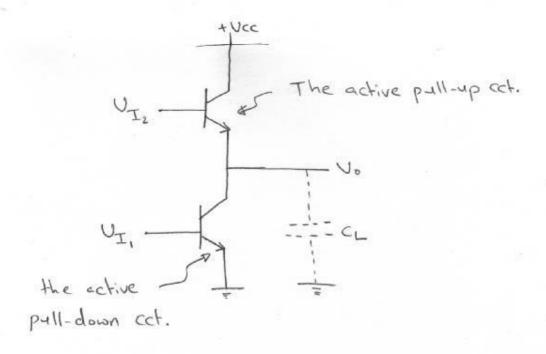

### Output Circuit of TTL !-

\* The C.E ofp Stage provides fast discharging of a load capacitance but rather Slow charging.

\* while the opposite is obtained in the C.C output stage, it provides fast charging of the load capacitance, but slow discharge of CL.

An optimum output stage will be the totem-pole output stage as shown:

UII and UIz are complementory inputs.

### (b) TTL with totem-pole output:

Case I: - when all inputs are high

\* when the input is high both Qz and Q3 are driven into Saturation, So Vo= Ucesat. = 0.2V.

Que should be off which is obtained by adding Diode

D. \* if D does not exist then:-

Ucz = UcEzi, + UBE3, = 0.2+0.7 = 0.9 U.

Which will turn Qu ON. and

TC4 = VCC - VCEU (SCL.) - VCED(Sat.) = 5-0.2-0.2

=46mA (excessive and wasted current).

therefore D was added so that

UD+ UBEY = UBY - UCE3Set. = 0.70.

: Ou and De are off since both of them require

1.4V to start conducting.

\* In the low output state, the gate can sink a load current (iL), provided that the value of iL doesn't exceed B\*2.93mA which is the maximum collector current that P3 can sustain while remaining in Saturation.

Case I when at least one input is low.

Assume that  $V_0 = \log ic(0) = 0.2V$  and one of the inputs becomes low.

Us across CL (load capacitance) remains momentainly at 0.2V.

Now Qu is in saturation and D is conducting,

UBu = UBEU(sat.) + UD+U0. = 0.7+0.7+0.2 = 1.60.

$$T_{CY} = \frac{U_{CC} - U_{CEH} - U_{D} - U_{o}}{o.1k} = \frac{5 - o.2 - o.7 - o.2}{o.1} = 39mA$$

$$B_{Fmin} = \frac{T_{CY}}{I_{BY}} = 16.05$$

choose BF716.05 then Qu is in saturation. As long as Qu is in Saturation, the output voltage rises as Qu is in Saturation, the output voltage rises exponentially towards Ucc with a very small time constant. The final value of the output voltage is:-

# TTL family with improved performance:

The TTL family is available in series emphasizing either high speed, low power, or both. These gates differ from one another in the numerical values of their resistors and in that some use schottky transistors.

#### TTL Series

| Symbol   | meaning                                             |

|----------|-----------------------------------------------------|

| S        | Schottky, high speed                                |

| LS       | schottky, low power                                 |

| -        | Standard (the previous one which have been studied) |

| There is | s the 74 series (o-70c) and the 54 series           |

| (-55-    |                                                     |

### Schottky TTL (745)%

\* The schottky diode is formed by bringing metal into contact with a moderately doped n-type semiconductor material.

\* The forward voltage drop of the schottky diade is 0.5V.

UCE =0.7-0.5=0.2V

\* In schottky TTL, transistors are prevented from saturation by connecting a schottky diode between base and collector of the transistor as shown above.

\* By avoiding saturation, the schotty transistor exhibits a very short turn off time.

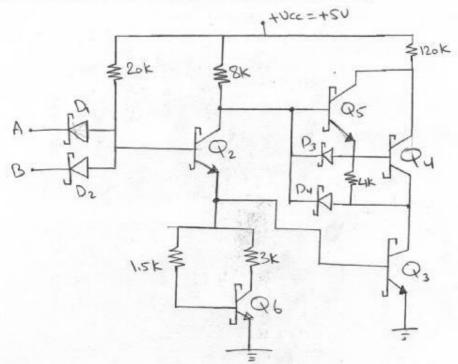

Schottky TTL NAND gate. Low power schottky TTL= (74LS)

A low-power schottky TTL (LSTTL) gate

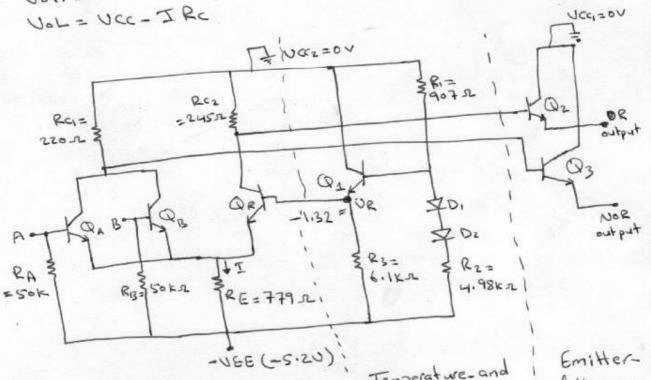

### Emitter-coupled Logic (ECL)

ECL is the fastest logic circuit family.

differential amplifier (Basic element of the ECL

UOH = UCC

Differential input amplifier

Temperature- and Voltage - componsated 1 bias network

follower outputs.

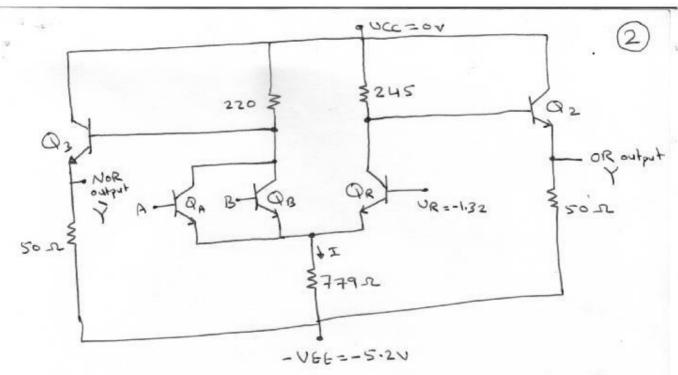

ECL basic gate COR and NOR

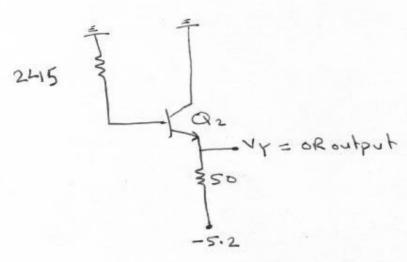

Simplified ECL in order to calculate the

At output Y (OR output):-

a) If all inputs (A and B in this case) are low then assume QA and QB are off and QR is conducting.

$$T = \frac{-2.02 + 5.2}{779} = 4.08 \text{ mA.}$$

then QA and QB are not conducting

\*If at least one of the inputs is high then its corresponding transistor (QA or QB) is conducting and QR is off.

assume B2 = 100

IB \* 245 + 0.7 + 50 \* IE = 5.2

IB \* 245 + 0.7 + 50 \* IB (1+100) = 5.2

IB = 0.85 mA.

VY = -0.908 = V(1) = VH

when all inputs (inputs A and B in this case) are then  $V_E = -0.908 - 0.7 = -1.608 U$   $T = \frac{-1.608 + 5.2}{0.779 \text{ K}} = 4.6 \text{ mA}.$

The emitter followers shift the level of the output signals by one UBG drop. These shifted levels are needed in order that one gate can drive another. This compatibility of logic levels at input and output is an essential requirement in the design of gate circuits.

#### ECL advantages

- 1- High speed, the highest of all logic families Since transistors do not saturate.

- 2 Complementary outputs are available which simplifies the logic design.

- 3- The differential nature of the circuit makes it less effected by noise.

### ECL disadvantages: -

1) The power dissipation is high as compared to other logic families.

#### MOSFET

3

\* MOSFET circuits are slower than corresponding

BJT circuits because of the parasitic capacitance,

\* The lower power dissipation and higher packing

density of Mos devices make them more

attractive and economical.

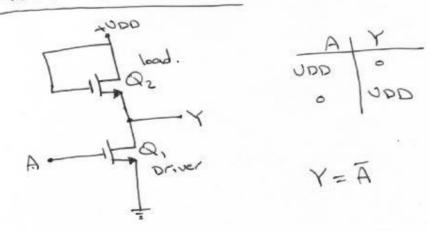

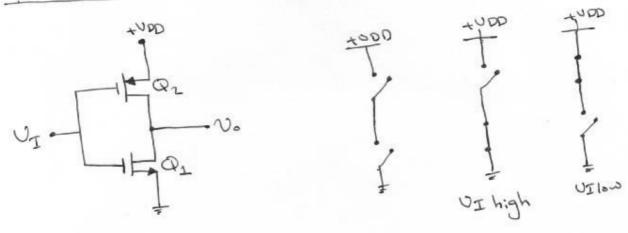

### MOSFET Inverter: -

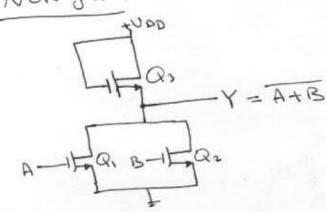

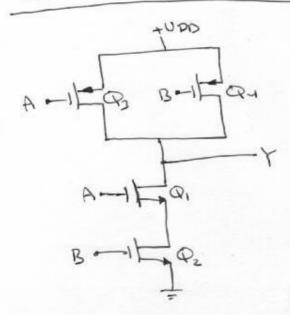

### MOSFET Logic gates:-

NOR gate:

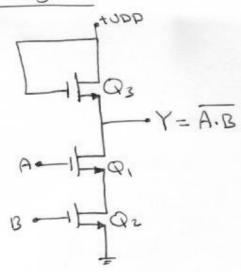

### NAND gate:

### Example:.

Implement the following function using NMOS logic.

## CMOS technology (complementary metal oxide semiconductor)

### CMOS Inverter !-

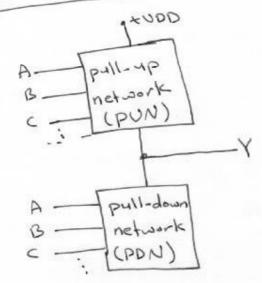

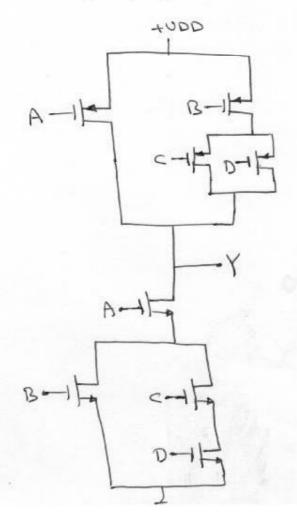

## Basic structure of CMOS Logic Circuits:

# PDN is constructed from only NMOS transistors, thus PDN is activated when the inputs are high.

\* PUN is constructed from only PMOS transistors, thus PUN is activated when the inputs are low.

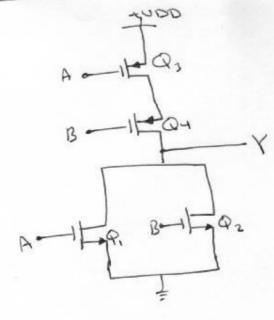

#### CMOS NOR gates-

### CMOS NAND gate:

Realize the following logic function using CMOS logic.

#### 501.:-

Y = A(B+CD) from which PDN is obtained To obtain the PUN

$$Y = \overline{A(B+CD)}$$

$$Y = \overline{A} + \overline{(B+CD)} = \overline{A} + \overline{B}, \overline{CD}$$

$$Y = \overline{A} + \overline{B}, (\overline{C}+\overline{D}).$$

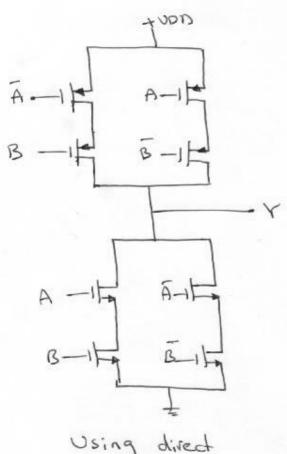

## Example:

Realize the Exclusive - OR Function: -Y= AB+ AB using CMOS logic.

#### Sol.: -

Y = AB+ AB from which PUN is obtained

Y = AB+ AB

Using direct method

H.w/ solve the same example using the duality property.

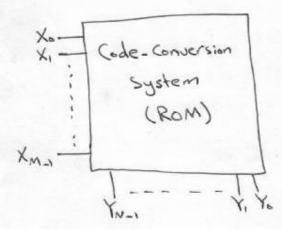

## Semiconductor Memories: -

# 1- Read only Memory: (ROM)

ROM is a memory that can be viewed as a combinational Logic circuit that contains fixed data patterns.

A ROM is a nonvolatile memory, meaning that the data is not lost with power supply switch off.

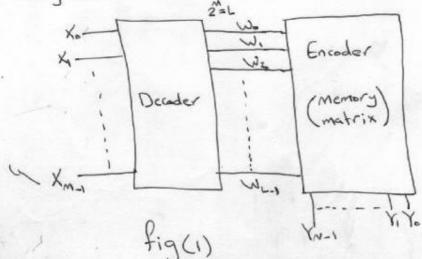

A ROM can be considered as a coole-conversion system as in the following block diagram:

which can be achieved as in the following block diagram:-

Consider a Gu-bit ROM arranged in 16 words of 2 U-bit each.

| X <sub>3</sub> | X2  | X | X. | word line      | Y3 Y2 Y1 Yo (olp as required) |

|----------------|-----|---|----|----------------|-------------------------------|

| 0              | 0   | 0 | 0  | Wo             |                               |

| 0              | 0   | 0 | ١  | w.             |                               |

| 0              | 0   | ١ | 0  | W <sub>2</sub> |                               |

| 0              | 0   | 1 | 1  | W3             | rearised                      |

|                |     |   |    | 1              | (ea                           |

|                |     |   |    | ,              | 27                            |

|                |     |   |    |                |                               |

|                |     |   |    | 1              |                               |

|                |     |   |    | 20.            |                               |

|                |     |   |    | 1              |                               |

|                | ) 1 | ١ | ١  | Wis            |                               |

Two-Dimensional addressing of a ROM

For a ROM with a large size, the previous decoding arrangment in fig(1) is impractical. The number of gates in the decoder becomes very large. Therefore 2-D addressing (X,Y) addressing is used.

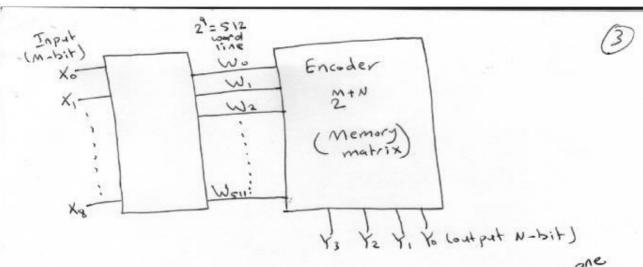

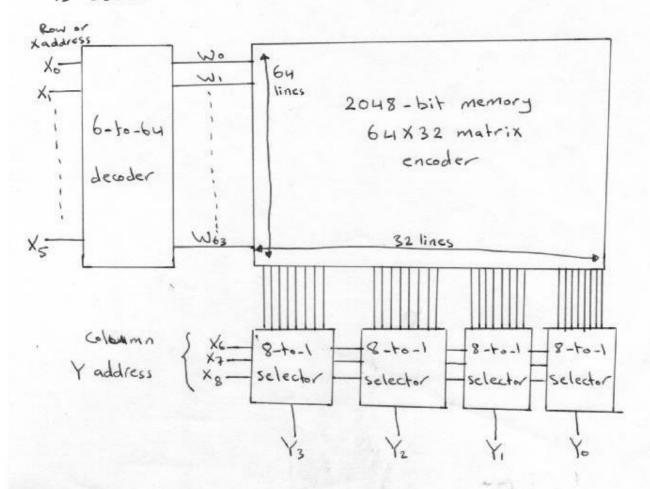

Example:

· 2048-bit (2Kb) with 4-output lines ROM

Sol. :-

if the block arrangement of fig(1) is used then

M=9, N=4

The decoder circuit will require S12 gates ( For each word line) which is impractical.

Therefore this 2-Dimensional addressing arrangment is used:

A 6-bit row address or Xaddress is used which gresults in 64 word lines (horizontal lines).

If 32 vertical lines are used in the memory matrix which results in 64×32 = 2048 bits.

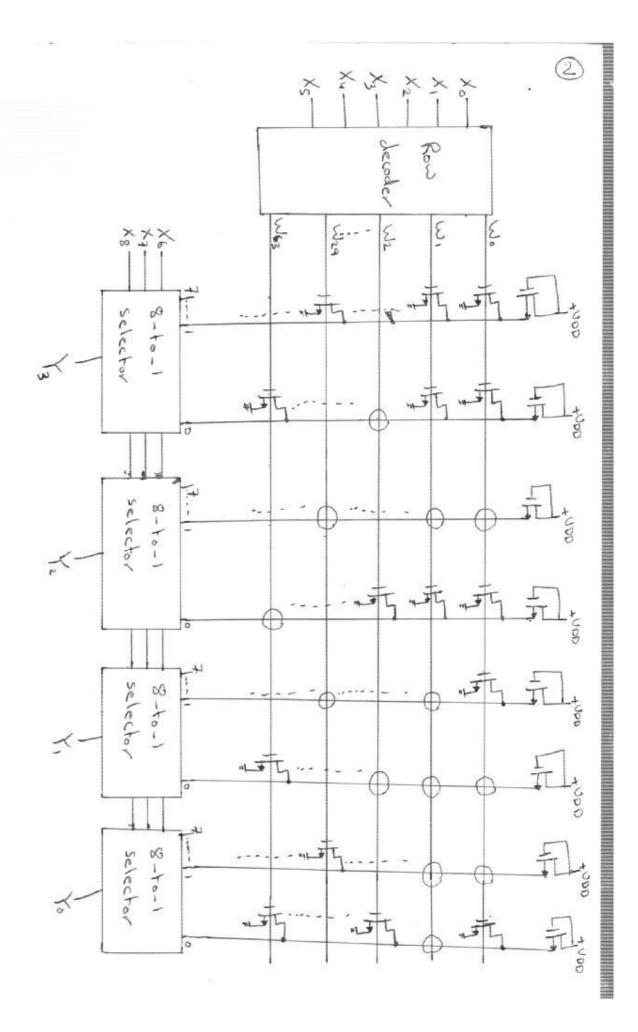

However, only four output lines are specified then four 8-to-1 line selectors are used. A 3-bit column address feeds each multiplexer.

## Row address Decoder

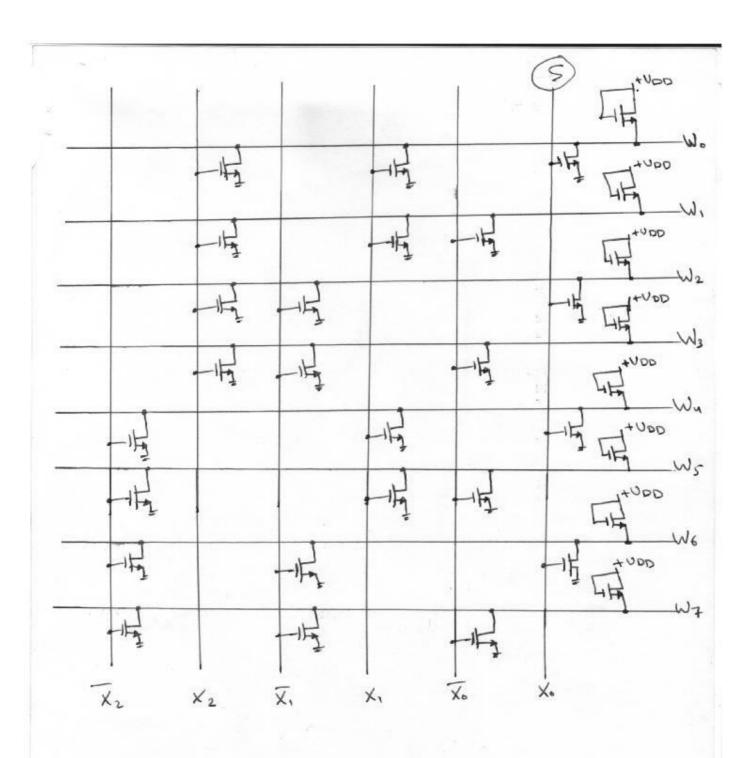

As an example let us take M=3 with the three address bits denoted Xo, Xi, and Xz and the 8-word lines denoted Wo, Wi, ---- W7.

From the truth table we can construct the Row address decoder in an array form using NMOS gates as in the following:-

| Xz | X | X.  | word line      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----|---|-----|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0  | 0 | 0   | w.             | Wo = X. X, X2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 0  | 0 | ١   | w,             | Wo = Xo + XI + Xz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 0  | 1 | 0   | W <sub>2</sub> | STATE |

| 0  | \ | 1   | W3             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| \  | 0 | 0   | WH             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 1  | 0 | - 1 | Ws             | WS = XO XIXZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1  |   |     | We             | $Ws = \overline{X}_0 + X_1 + \overline{X}_2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1  | ١ | 1   | W7             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|    |   |     |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

# Memory matrix (encoder)

| 1   | Xg | X   | X6  | Xs  | X4 | X3  | X2 | X, | X. | word line | Y | 3 Y2 | Y, - | Y0 |  |

|-----|----|-----|-----|-----|----|-----|----|----|----|-----------|---|------|------|----|--|

| 80. |    |     |     | 0   |    |     |    |    |    | w.        | 0 | 0    | \    | 0  |  |

|     | 0  | 0   | 0   | 0   | 0  | 0   | 0  | 0  | 1  | W,        | 0 | 0    | 1    | 1  |  |

|     |    |     | 0   | . 0 | 0  | 0   | 0  | ١  | 0  | W2        | 1 | 0    | 1    | 0  |  |

|     | 0  |     |     |     |    | 1   |    |    |    | 1         |   | 1    |      |    |  |

|     |    |     |     | i   |    | ١   |    |    |    | 1         |   | 1    |      |    |  |

|     |    |     |     | 1   |    | ,   |    |    |    | `         |   | 1    |      |    |  |

|     |    |     |     | 1   |    | 1   |    |    |    | 1         |   | X    |      |    |  |

|     |    |     |     | 1   |    |     |    |    |    | 1         |   | 1    |      |    |  |

|     |    |     |     | 1   |    |     |    |    |    | X.        |   | 1    |      |    |  |

|     |    | 0   | 00  | •   | 1  | 11  | 1  | ١  | 1  | W63       | 0 | 1    | 0    | O  |  |

|     | (  | 0   | 0 1 | 1   | 0  | 0   | 0  | 0  | 0  | wo        | 0 | 1    | 0    | 1  |  |

|     |    |     |     |     | ^  | 00  | 0  | 0  | 1  | W,        | 0 | 1    | ١    | 1  |  |

|     | (  | 2 ( | 0 1 | ;   | O  |     |    | _  | 1  | ,         |   | 1    |      |    |  |

|     |    | 1   |     | 1   |    |     |    |    |    | ;         |   | ,    |      |    |  |

|     |    | 1   |     | 1   |    |     | ,  |    |    |           |   | 1    | - 7  |    |  |

|     |    |     | - 1 | 1   | 0  | 11  | 1  | 0  |    | W29       | 0 | 1    | 1    | 0  |  |

|     |    | 0   | 0   | 1   | -  | , , |    |    |    | ' 1       | , |      |      |    |  |

|     |    |     |     |     |    | ,   |    |    | 1  | ,         |   | 3    |      |    |  |

In a semiconductor memory an array of storage cells is used in constructing a RAM.

Eeach cell to is holding I bit of data.

ARAM is a voltatile memory, which means that all stored information is lost when power supply is turned off.

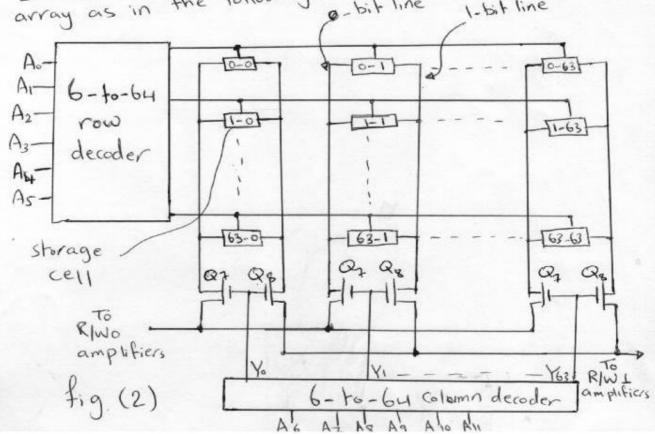

Two-Dimensional addressing of a RAMI-

A great economy of the number of gates in the decoder circuit is obtained by arranging the memory cells in a two-dimensional array.

For example: - A HK bit RAM is organized in a 64x64 array as in the following: - bit line 1-bit line

figure (2) shows the organization of a 4096 9 word-by-1 bit RAM.

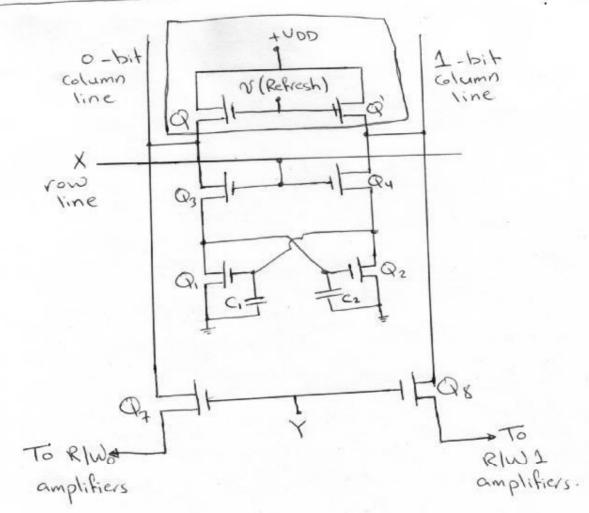

RAM Cells :-

@ Static MOS RAM +UDD 1-61 data 0-617 line Q6 11 data line 6 Mos memory cell (i-j) 07 1 [a8 DOUTE · LIKO" 4Kas · Dout Doute writest Pa RIWO RIW 1 amplifiers amplifiers. OF RIW

- \*To select a cell its X and y address should 5. be excited (2-Dimensional) addressing.

- \* QIT and QIO form an AND gate with inputs WE and Din. also QIT and Qq form an AND gate with inputs WE and Din.

where WE or R/W = write enable

Din = Data input.

Dout = Data output.

## CaseI

(write a 1 in the cell)

- O address the cell (Xi=1 and Yj=1) so that Q7, Q8, Q5 and Q6 are conducting.

- 2) set WE=1, Din=1 and Din=0

\* then QIZ and QIO are ON and Qq is off.

Hence the 1-bit data line is grounded and o-bit data

line goes to UDD through load QII.

- \* Thus node Nz is effectively grounded.

- \* So Qi is cutoff and Ni rises to VDD.

- \* No is fied to the gate of Q2 therefore Q2 is held ON and N2 is maintained at OV.

- \* when the address is removed (Ps, Q6, Q7 and Q8 are Off), Q2 is ON, Q1 is off, and a 1 has been written into the selected memory Cell.

## Case II (read a 1 stored in a memory cell)

6

- O Set Xi=1 and Yj=1

- 2) assume that a 1 is stored in this cell so Qz is ON and Qi is OFF (Nz is at OV and Ni is at UDD).

- 3 Set WE = 0.

- \*Then Qit is Off and hence Qio and Qq aire non conducting.

- \* So the 1-bit data line and the O-bit data line are connected to UDD through load Qiz and Qii respectively.

- \* since Q2 is ON (N2 at OV) then the 1-bit line is effectively grounded.

- \* therefore Qu is Off and Dout = VDD (logic 1).

- \* Since Qi is Off then O-bit data line is at UDD.

- \* therefore Q13 is ON and Dout =0

So we have read I stored in cell (i,j).

In the Dynamic RAM cell, information is stored as charge on the two capacitors C1 and C2.

If a I is written in the Cell then C2 is charged to UDD and C1 is charged to UDD and Q1 is off.

In DRAM the capacitors which store the information will discharge slowly because of the leakage currents and information may be list.

Therefore DRAM require periodic refreshing to regenerate the data stored on capacitors.

The two transistors (Q and Q') are added to refresh each cell in a given column.

If we have a RAM with 64 columns then 64 of such circuitry (Q and Q) is needed to refresh acell in that coloumn.

N is a pulse of less than I Msec occurring about every 2 msec.

If X, is high and v is also high then row(1) will be refreshed simultaneously.

Because X, is high then Qz and Qu are ON, and because or (Refresh) is high then Q and Q' are ON.

Assume that QI is Off and Qz is ON (storing a1).

Then during the refresh interval a current will

Flow in Q and Q3 charging C2 toward VDD

and since QI is Off all the current from VDD

is directed toward C2.

As for the current in Q' and Qu then C will not be charged because Qz is conducting so the cell is restored to its original state.